Method for generating system model and method transmitting data in same

A technology for transmitting data and models, applied in the field of transmitting data

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

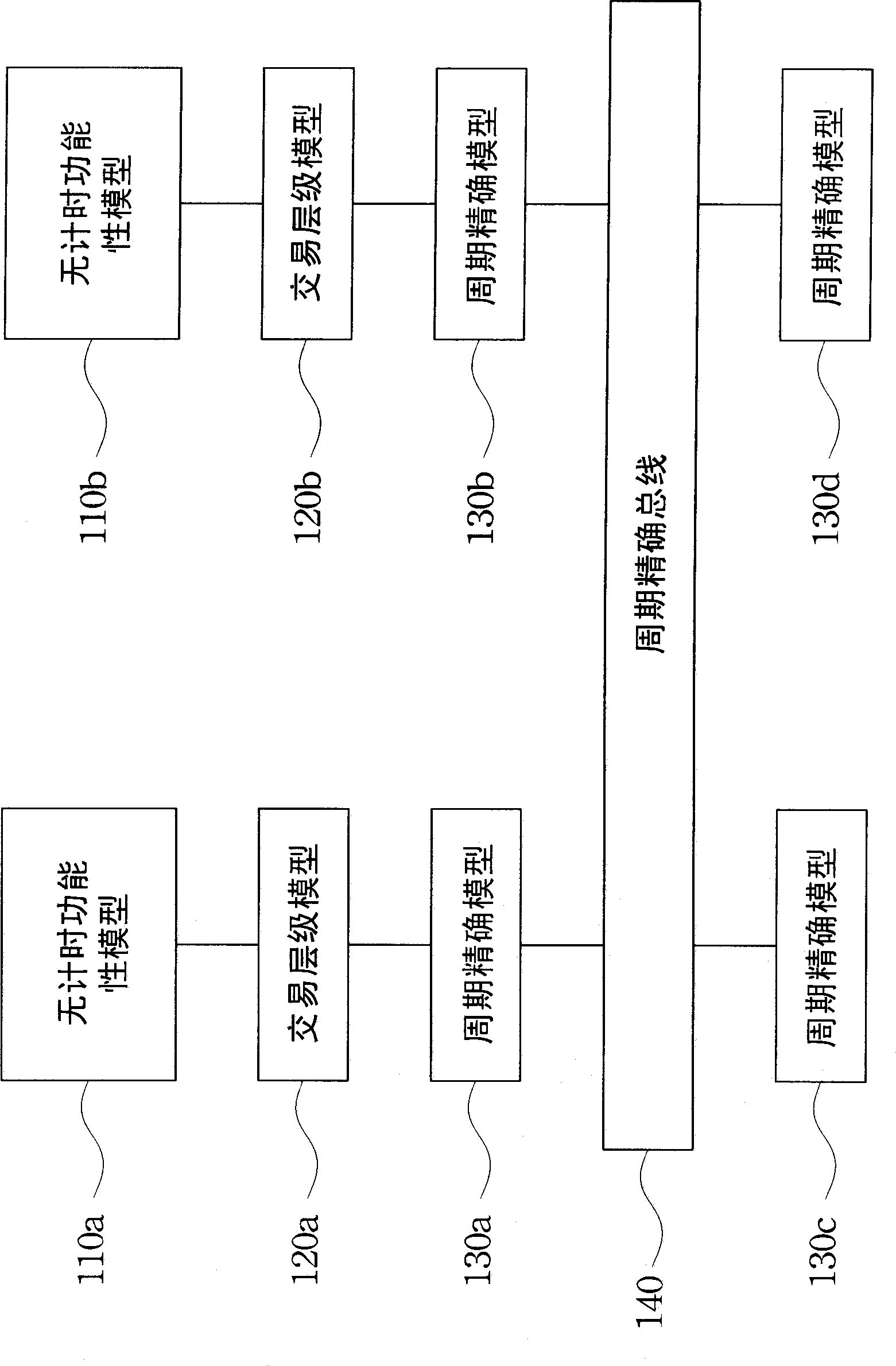

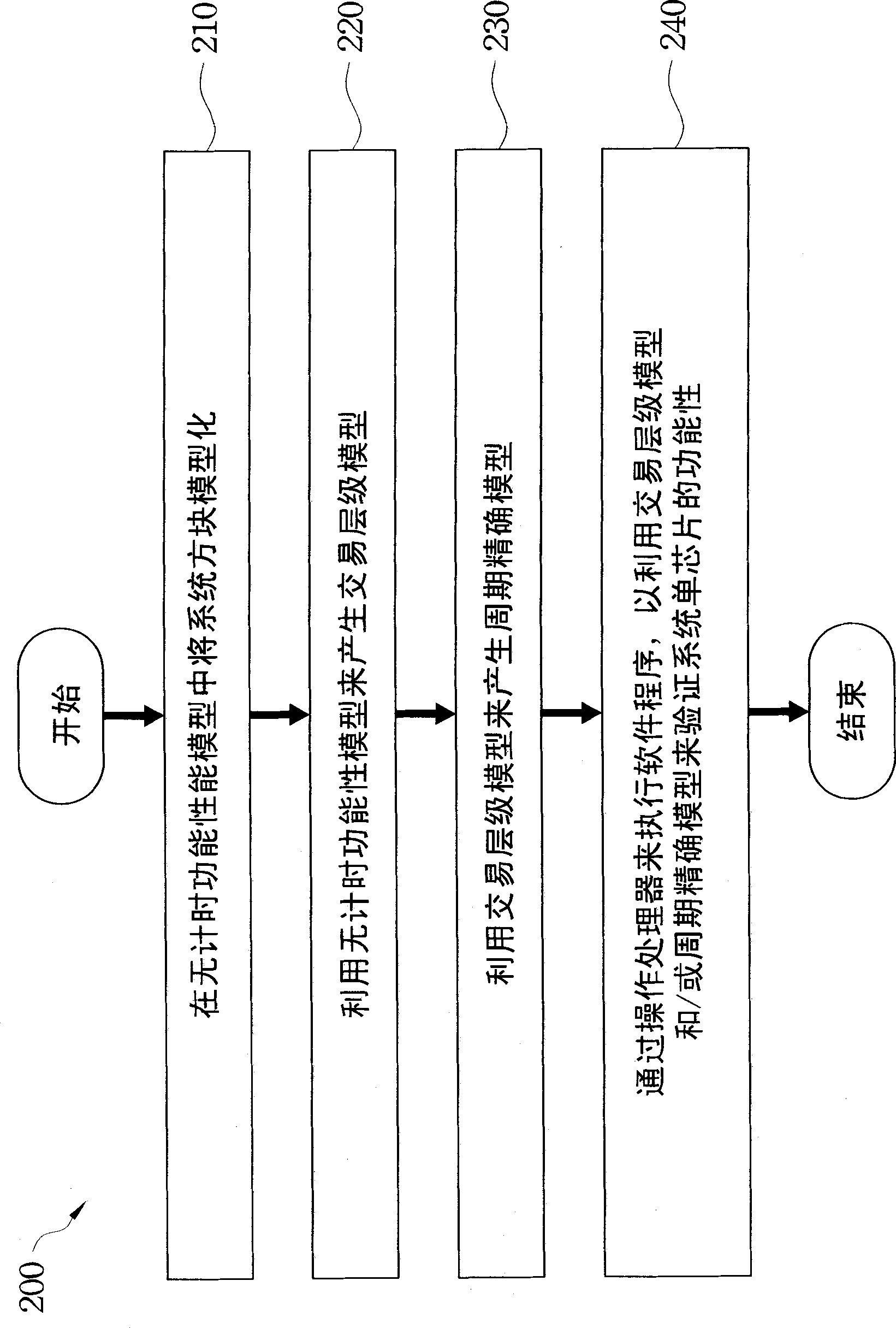

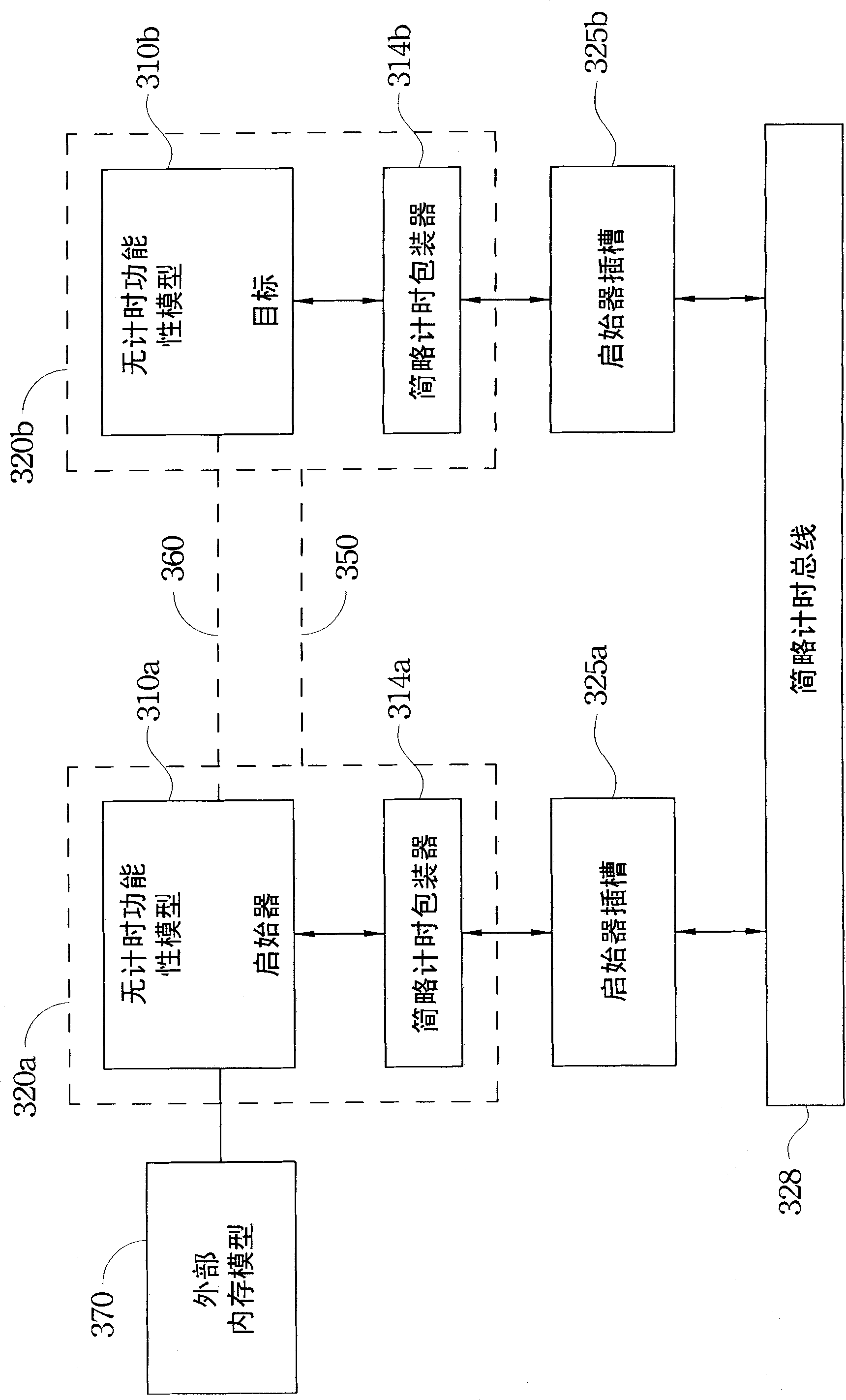

[0061] Software development in RTL is challenging due to the slow simulation speed of RTL design. Simulation speeds in the millions of cycles per second range are instructive for software development, while RTL typically provides simulation speeds of less than 100 to 200 cycles per second. The use of hardware accelerators and emulators has increased rapidly, reaching the cycles per second throughput that leads to software development. However, hardware accelerators or emulators can only be used if an RTL or gate-level design is available. Before the RTL design information is ready, it is too late in the design cycle to make architectural changes to develop software that performs optimally and has precise functionality. A lot of project plans are cancelled or too late due to delays in software development. Therefore, there is a need for a platform or tool to develop software prior to design at the RTL or gate level, and this platform or tool is provided in various embodiments...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com