Test method of high-precision dynamic comparator and test circuit thereof

A technology of dynamic comparator and test method, which is applied in the direction of measuring electrical variables, measuring current/voltage, instruments, etc., can solve problems such as time-consuming and energy-consuming, and achieve simple and fast results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

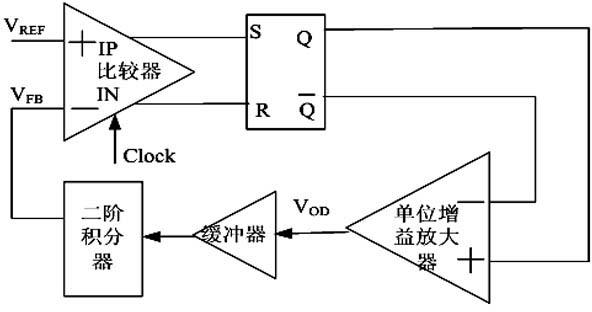

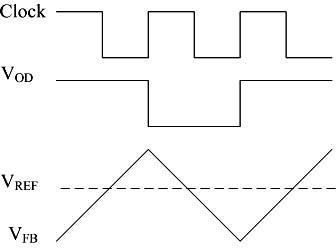

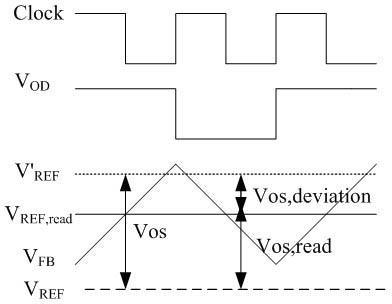

[0014] The present embodiment provides a method for testing a high-precision dynamic comparator. The method first judges the output state of the comparator through a clocked SR latch, and inputs the judged output signal into a unity-gain amplifier; secondly, provides a The second-order integrator provides a feedback voltage for the comparator after positive and negative integration of the output signal of the unit gain amplifier through the buffer. .

[0015] In order to realize the above-mentioned method, the present embodiment provides a test circuit of a high-precision dynamic comparator, which is characterized in that, comprising: a comparator; a clocked SR latch; its input terminal is connected to the output terminal of the comparator; a unity gain amplifier having an input connected to the output of the clocked SR latch; and a second order integrator having an input connected to the output of the buffer and an output providing a feedback for the comparator Voltage . ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More