Level shift circuit and semiconductor device

A technology of level shifting circuit and level, which is applied in the direction of electrical components, logic circuit connection/interface layout, logic circuit coupling/interface using field effect transistors, etc., and can solve the problem that the level shifting circuit 120 cannot operate normally.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

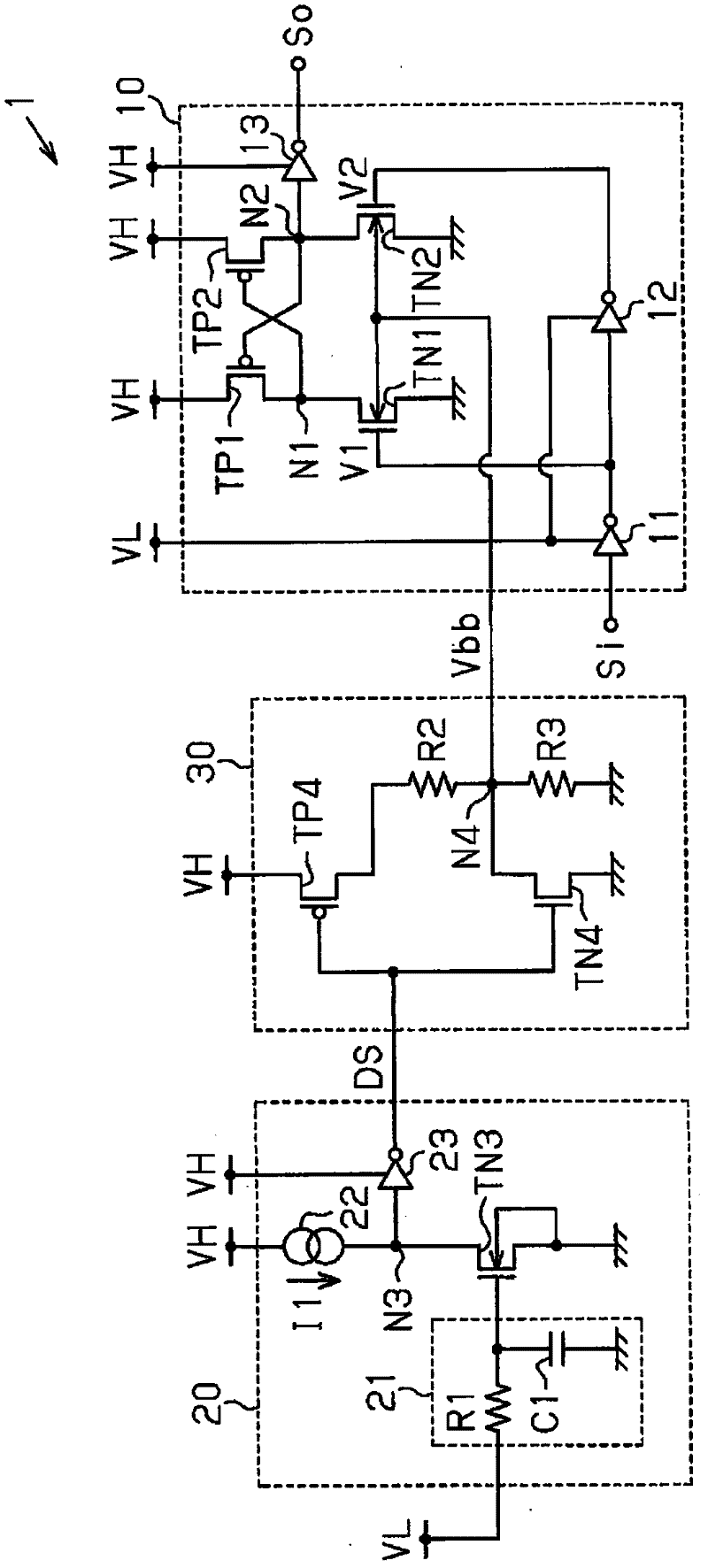

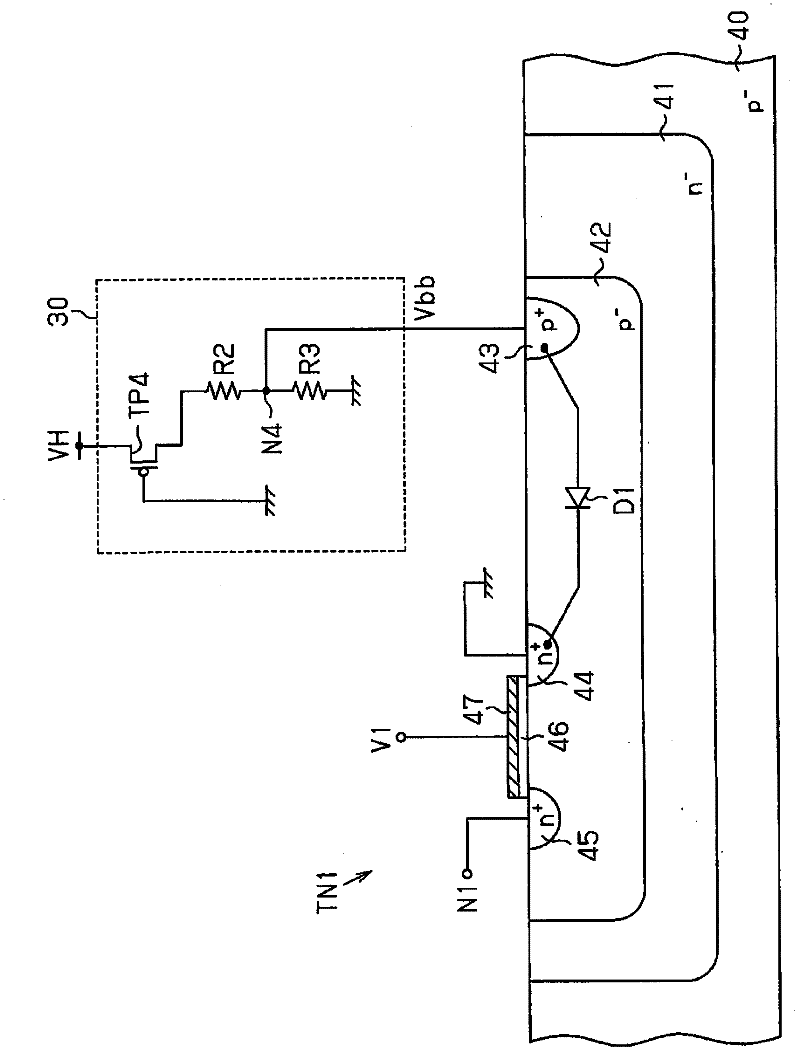

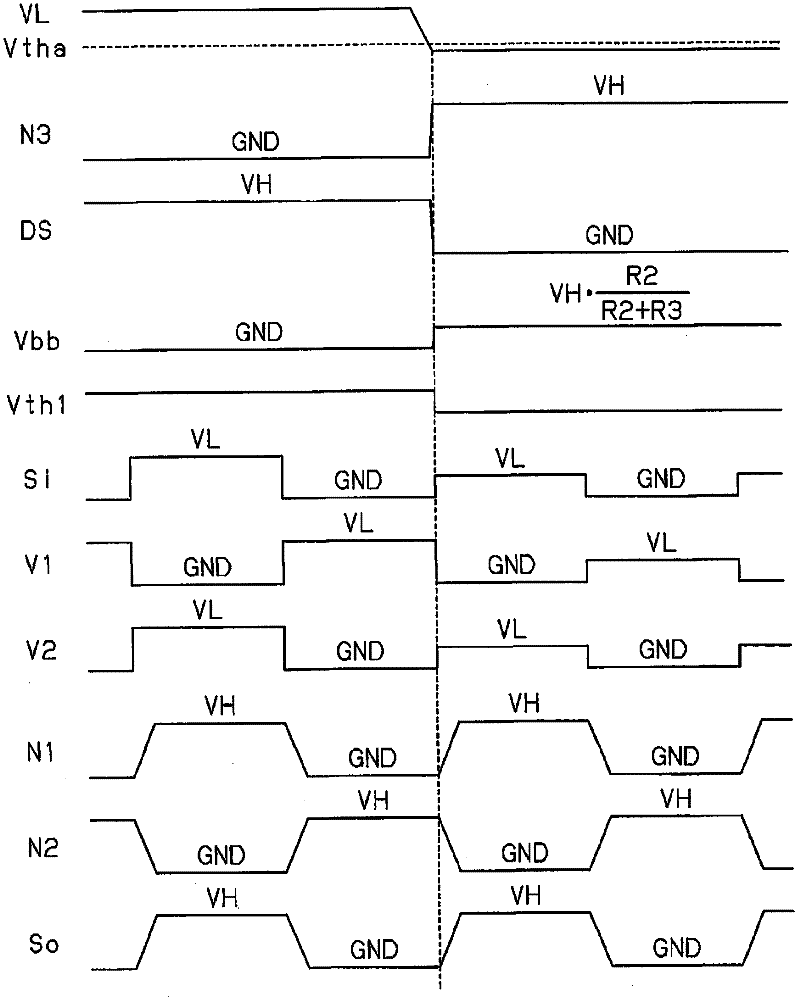

[0032] will now refer to Figure 1 to Figure 3 The first embodiment will be described.

[0033] The level shift circuit 1 converts the input signal Si having a signal level of a reference voltage (low potential voltage) and a first high potential voltage VL into a signal level having a reference voltage GND and a second high potential voltage VH (which is higher than the first high potential voltage) The output signal So of the signal level of the voltage VL). Hereinafter, for brevity, the level of the first high potential voltage VL is referred to as H1 level, the level of the second high potential voltage VH is referred to as H2 level, and the level of reference voltage GND is referred to as L level.

[0034] The level shifting circuit 1 includes a level conversion unit 10 , a detection unit 20 and a control unit 30 . The level converting unit 10 converts the input signal Si at the H1 level into the output signal So at the H2 level. The detection unit 20 detects a decrea...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More