FPGA (field programmable gate array) interconnection line time-delay acquiring method and system utilizing same

An acquisition method and acquisition system technology, which is applied in the field of FPGA interconnect line delay acquisition, can solve the problems of heavy workload and inaccurate simulation, and achieve the effect of high accuracy and easy acquisition

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

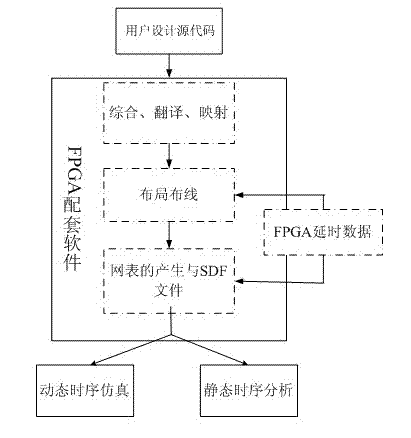

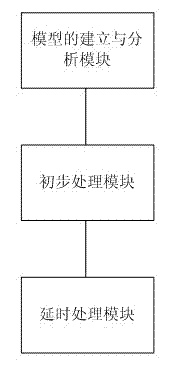

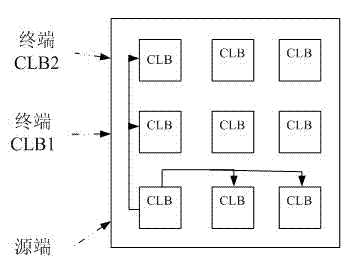

[0024] combine figure 2 , image 3 , Figure 4 with Figure 5 , to further describe the embodiments of the present invention.

[0025] Generally speaking, the interconnection line includes a programmable configuration selector (MUX), an inverter (inverter) on the line, and a physical line. Most FPGAs adopt a programmable interconnection line model of hierarchical interconnection. In this model, there are usually three types of connections in the wiring channel, namely, the short line (Short Line) of the adjacent high-speed interconnection level, and the local connection line. For Dividable Long Line at the level and Long Line at the global level, the configuration selector acts as a switch for connecting between different lines.

[0026] The interconnection delay is mainly affected by the structure, drive and load of the interconnection. The drivers and loads of the three types of interconnections, short-term, divisible long-term, and long-term, are different. Therefore, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More