On-chip multi-core data transmission method and device

A technology of data transmission device and data transmission method, which is applied in the direction of electrical digital data processing, digital computer components, instruments, etc., can solve the problems of limiting and increasing the calculation speed, and achieve the effect of alleviating the increase of network delay and alleviating the negative impact

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

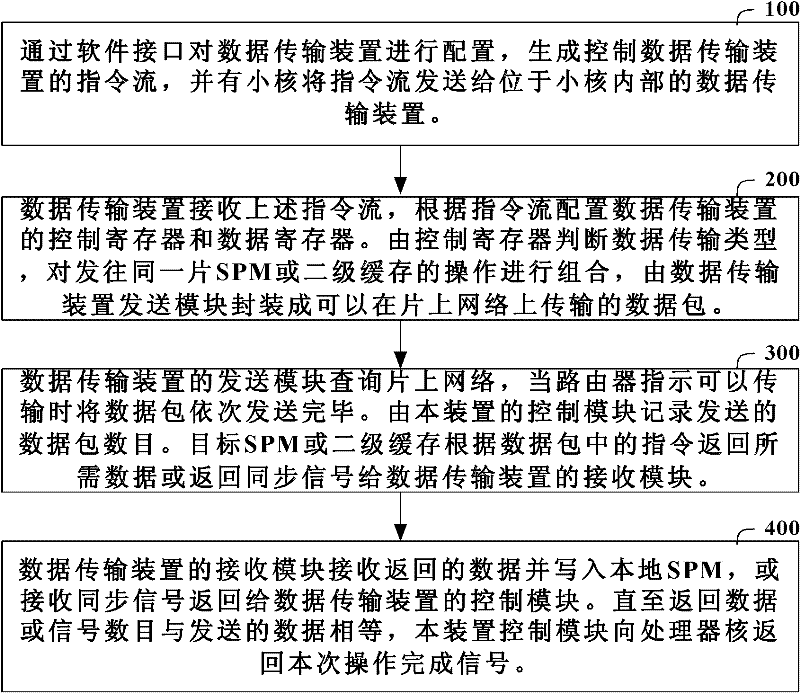

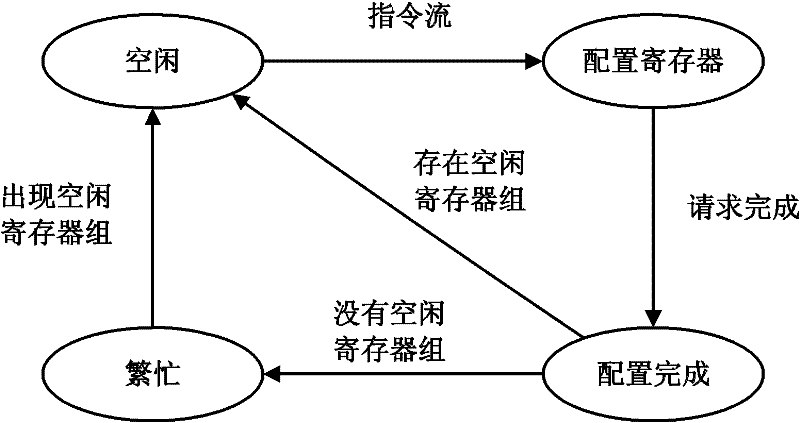

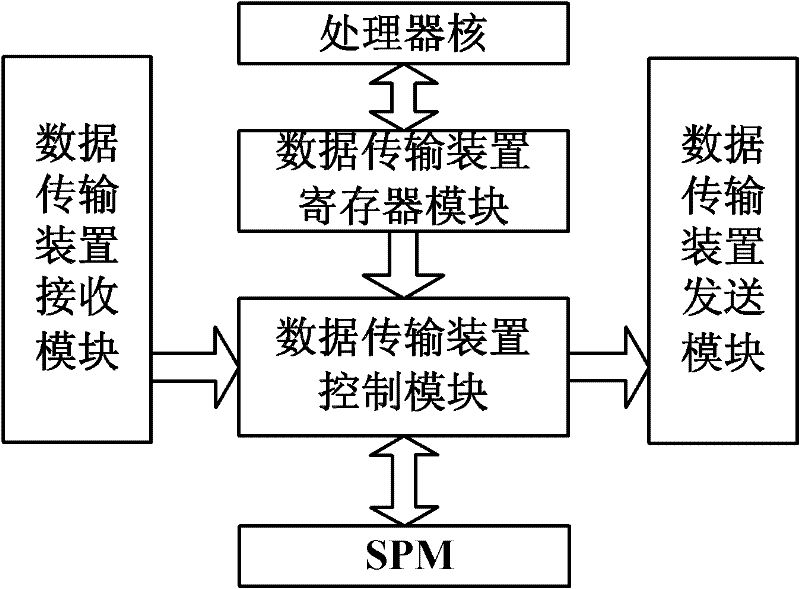

[0056] In order to make the purpose, technical solution and advantages of the present invention clearer, an on-chip data transmission method and device of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0057] In order to improve the memory access bandwidth, the data required by the parallel application of large-scale data transmission should have strong continuity and regularity, which is beneficial for programmers not to schedule data at the storage level. Therefore, the present invention provides programmers with a The programmed on-chip data transmission method enables parallel and large-scale transmission of data between the first-level cache and the second-level cache, and can transmit data between the first-level cache.

[0058] The present...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com