Method for rapidly creating integrated circuit test program package

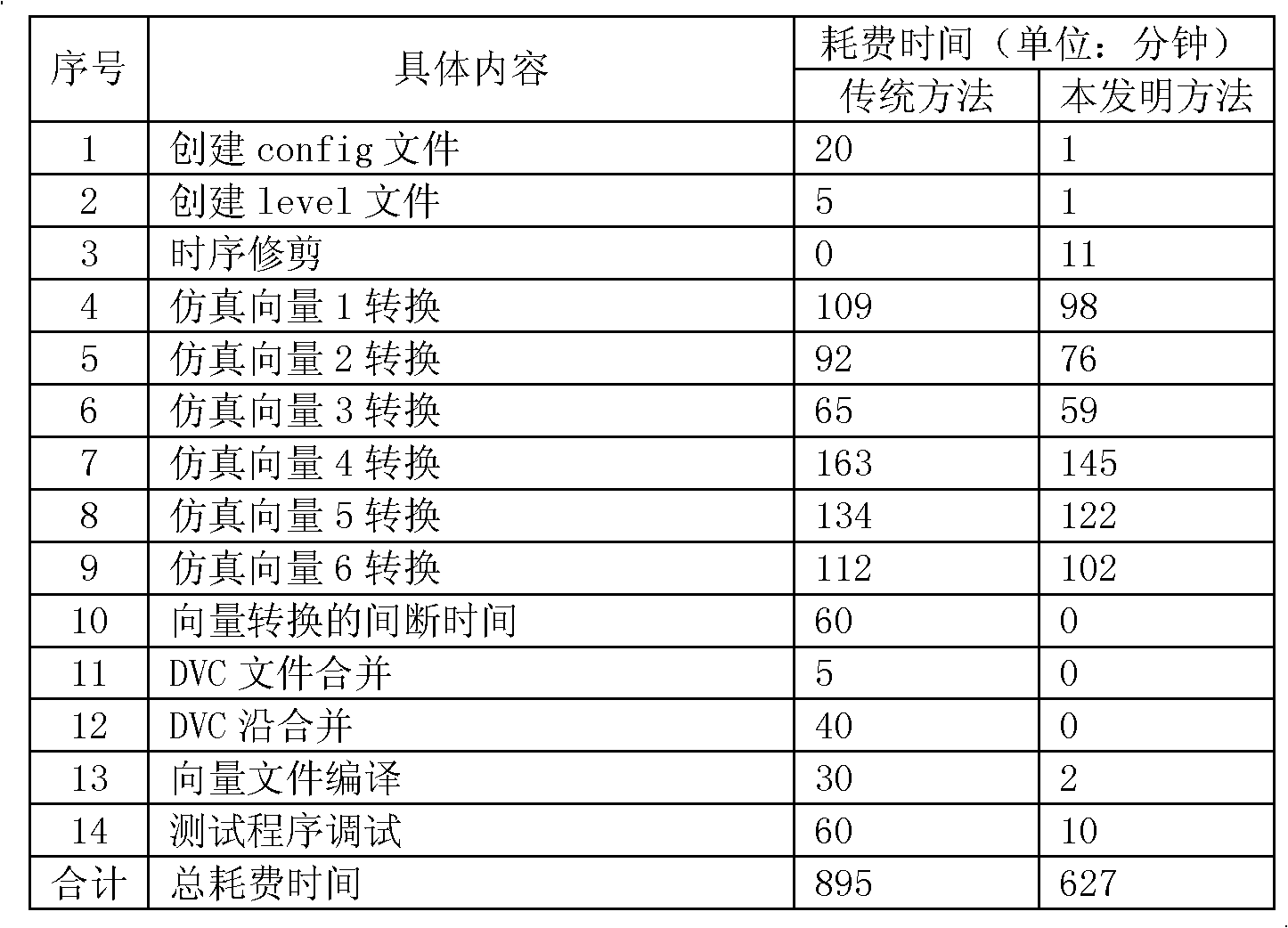

A test program and integrated circuit technology, which is applied in the direction of electronic circuit testing, measuring electronics, measuring devices, etc., can solve the problems of difficult test program debugging and low test development efficiency, so as to save interruption time, avoid manual intervention, and reduce workload Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

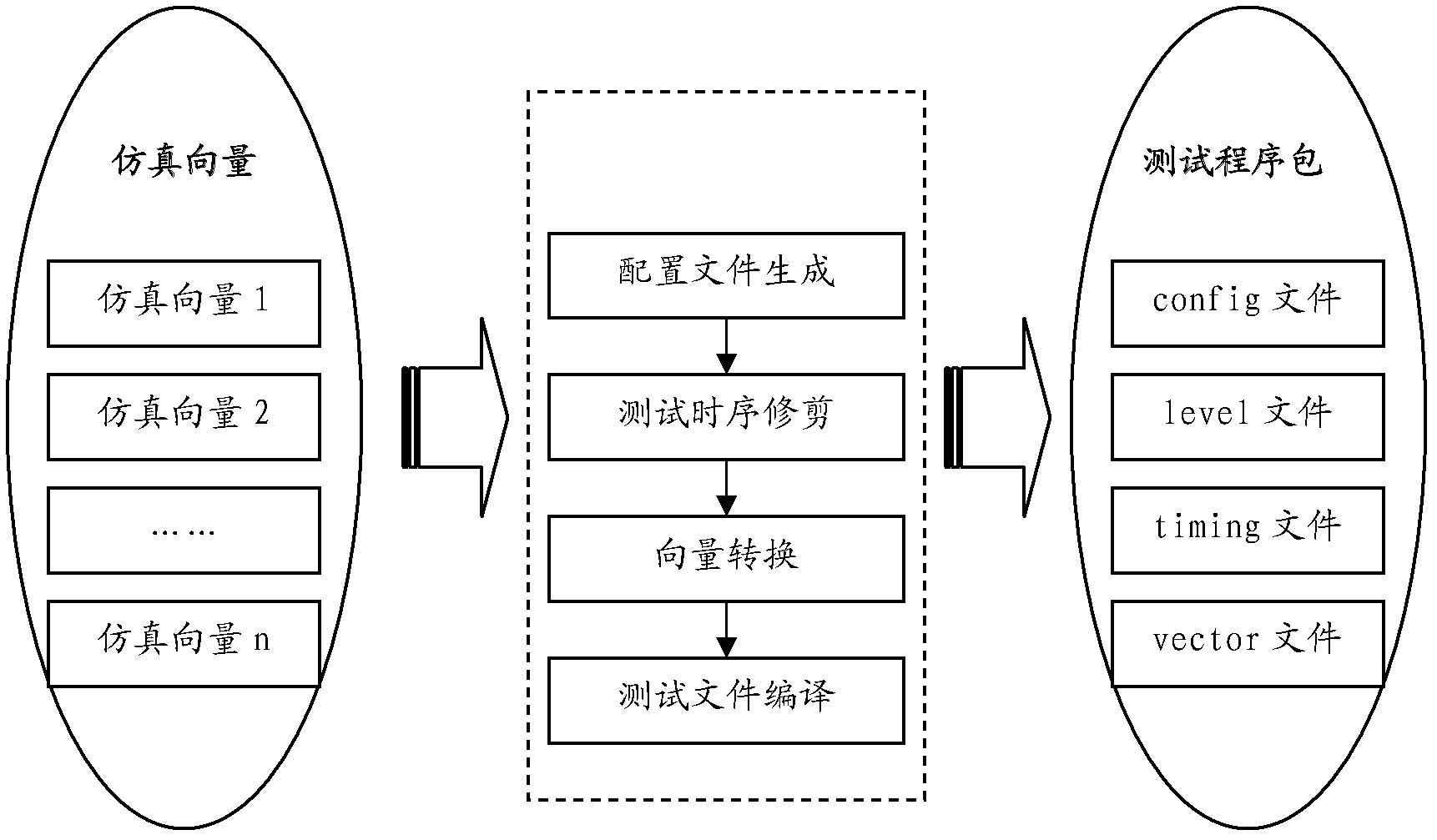

[0015] see figure 1 , the present invention creates the step of the fast method of integrated circuit test program package and comprises the following four parts:

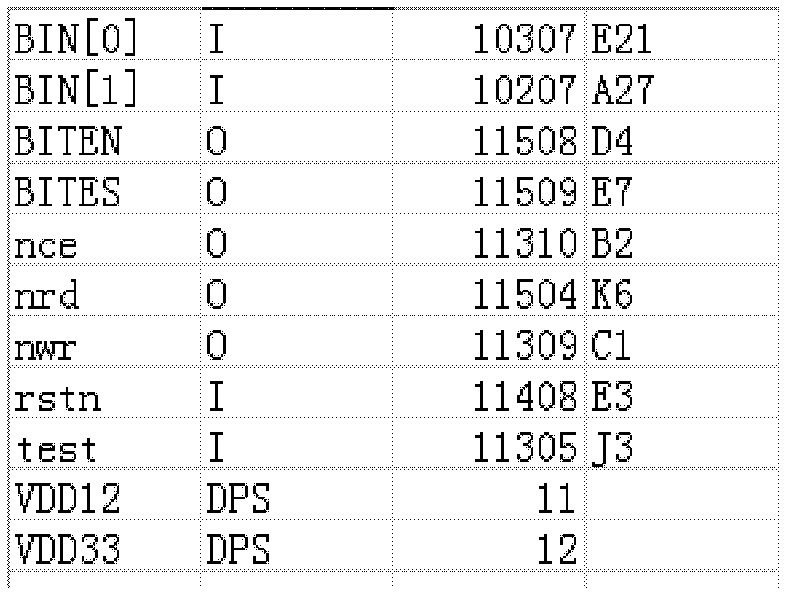

[0016] The first part is configuration file generation. Configuration file generation first extracts the signal name from the VCD simulation vector, creates a configuration file template, according to the pin number or coordinate number, input / output attribute in the DUT product manual (Specification), and the ATE hardware channel used in the design of the test interface board, Write in the template to form a configuration file, the format is in the form of a list, such as error! Reference source not found. shown. Finally, use the configuration file to generate the config file and the level file that the ATE test software can call directly.

[0017] The second part is the pruning of test timing. The test sequence pruning mainly uses four optional pruning methods to prune the VCD simulation vector according to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More