Sampling hold circuit structure for realizing offset elimination function

A sample-and-hold circuit and circuit structure technology, applied in the direction of physical parameter compensation/prevention, etc., can solve the problems of analog-to-digital converter precision decline, large v0, difficult control of Vos1, etc., to eliminate offset voltage errors, reduce difficulty, and ensure The effect of precision

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

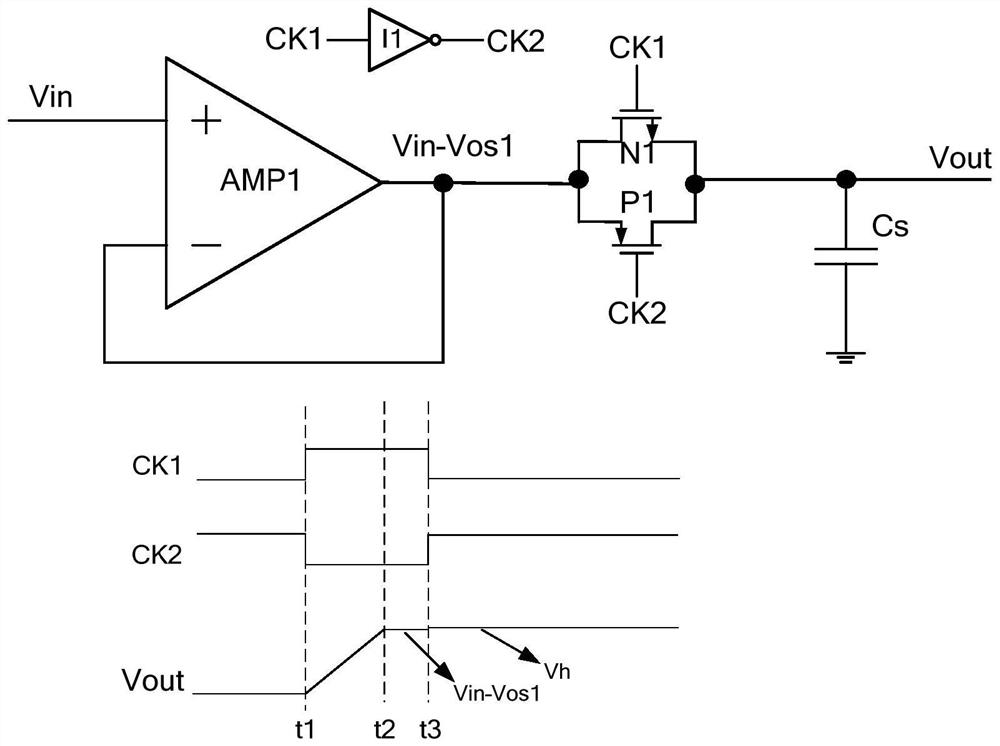

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

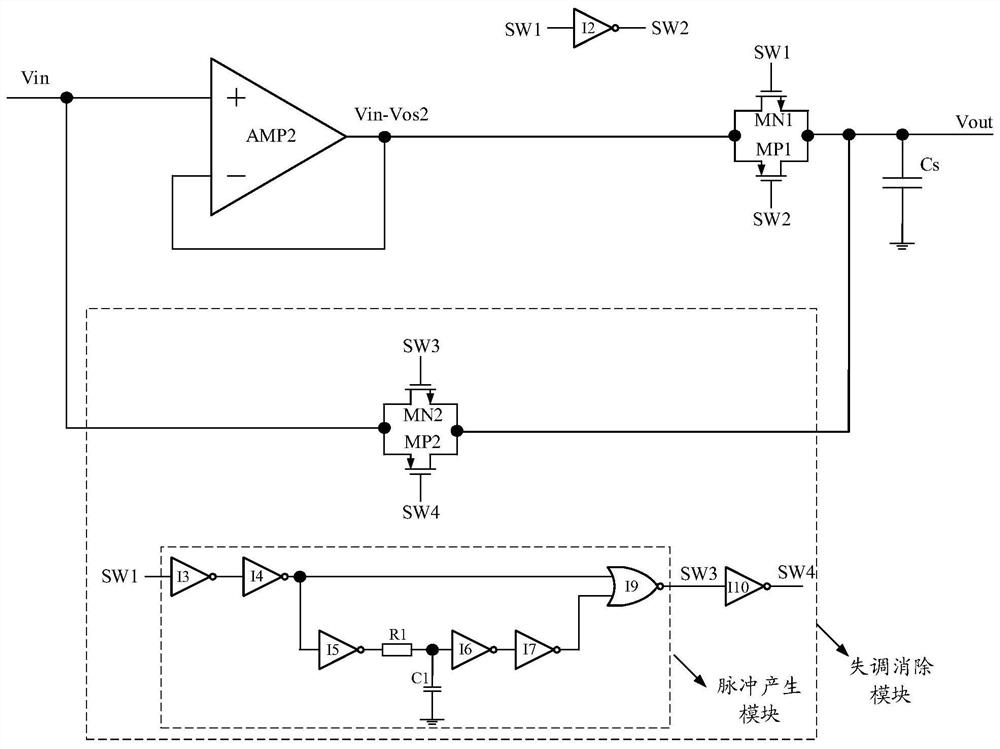

[0018] In order to describe the technical content of the present invention more clearly, further description will be given below in conjunction with specific embodiments.

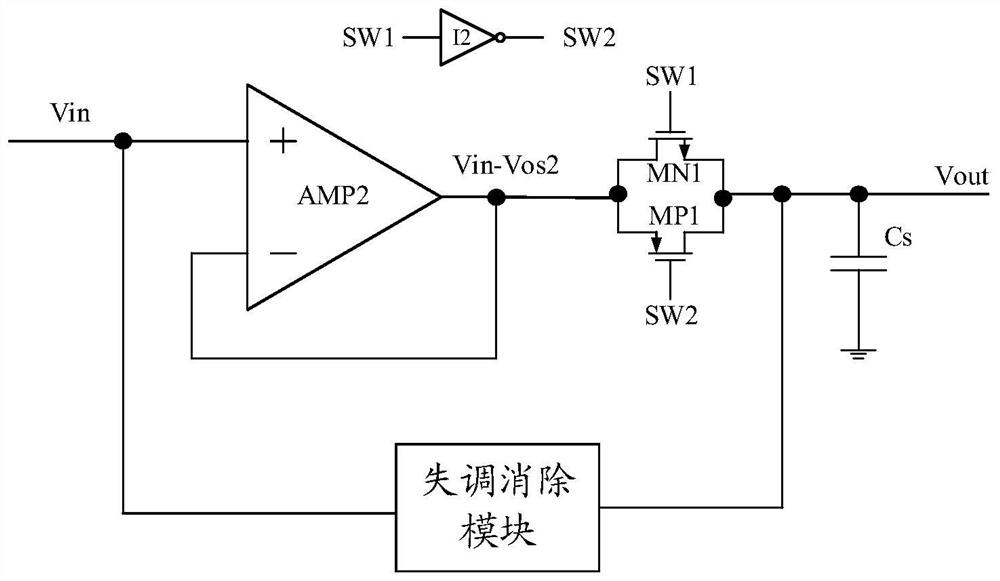

[0019] The sample-and-hold circuit structure of the present invention that realizes the offset elimination function includes an operational amplifier, a first CMOS transmission gate module, and an offset elimination module. The positive input terminal of the operational amplifier is connected to the input signal, and the output terminal is connected to the first CMOS transmission gate module. The gate module is connected, and the negative input terminal of the operational amplifier is connected with the output terminal as a unity gain buffer, and the two ends of the offset elimination module are respectively connected to the positive input terminal of the operational amplifier and the output terminal of the CMOS transmission gate module. connected, the offset elimination module is used to eliminate the influ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More