High voltage isolation structure based on silicon on insulator

A technology of silicon-on-insulator and isolation structure, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problem that the sidewall oxide layer cannot be made very thick, shorten the thermal oxidation time, overcome the uneven voltage, Flexible Adjustable Effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

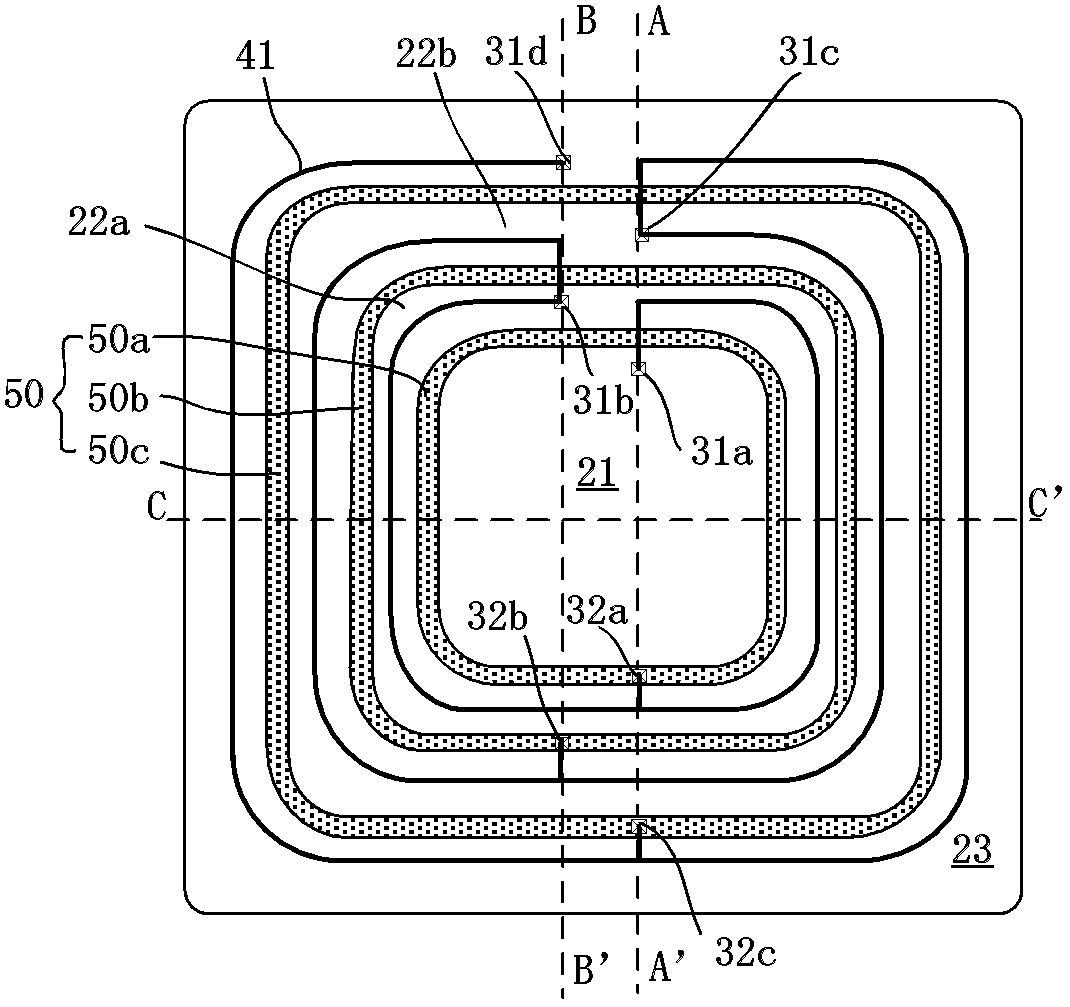

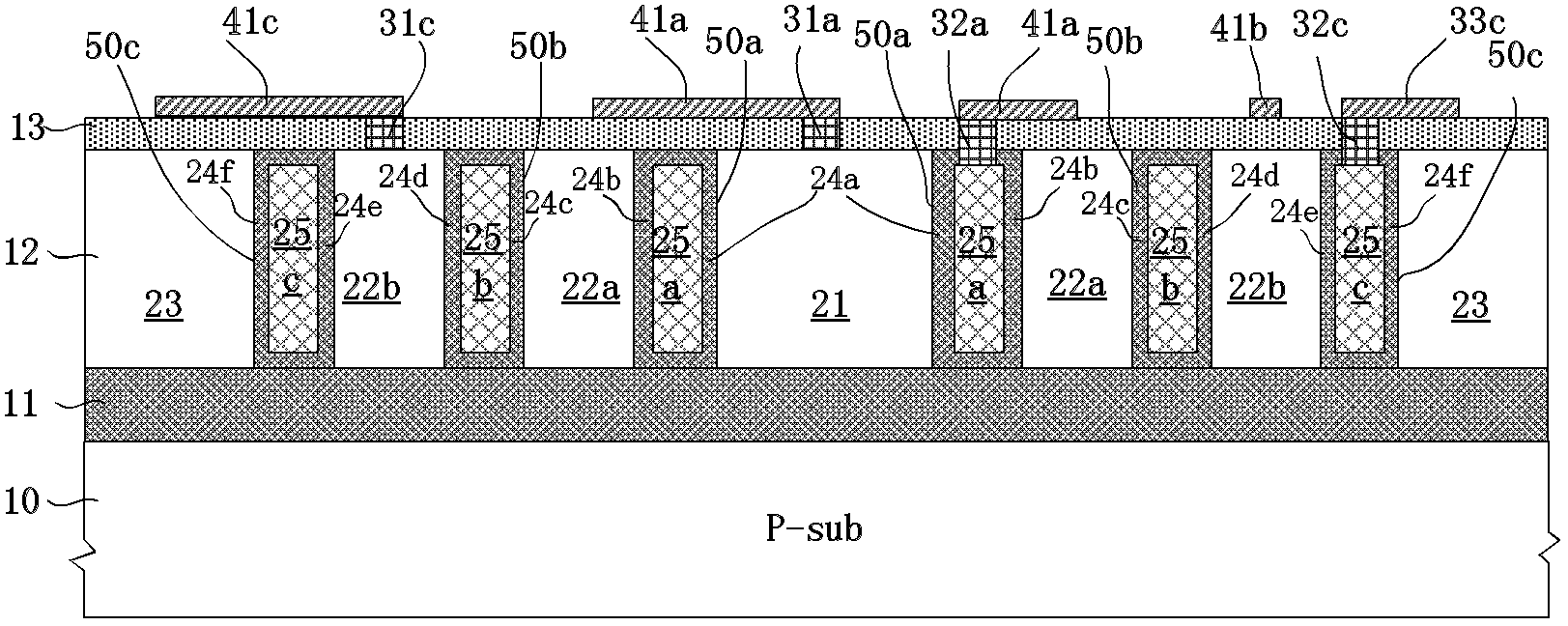

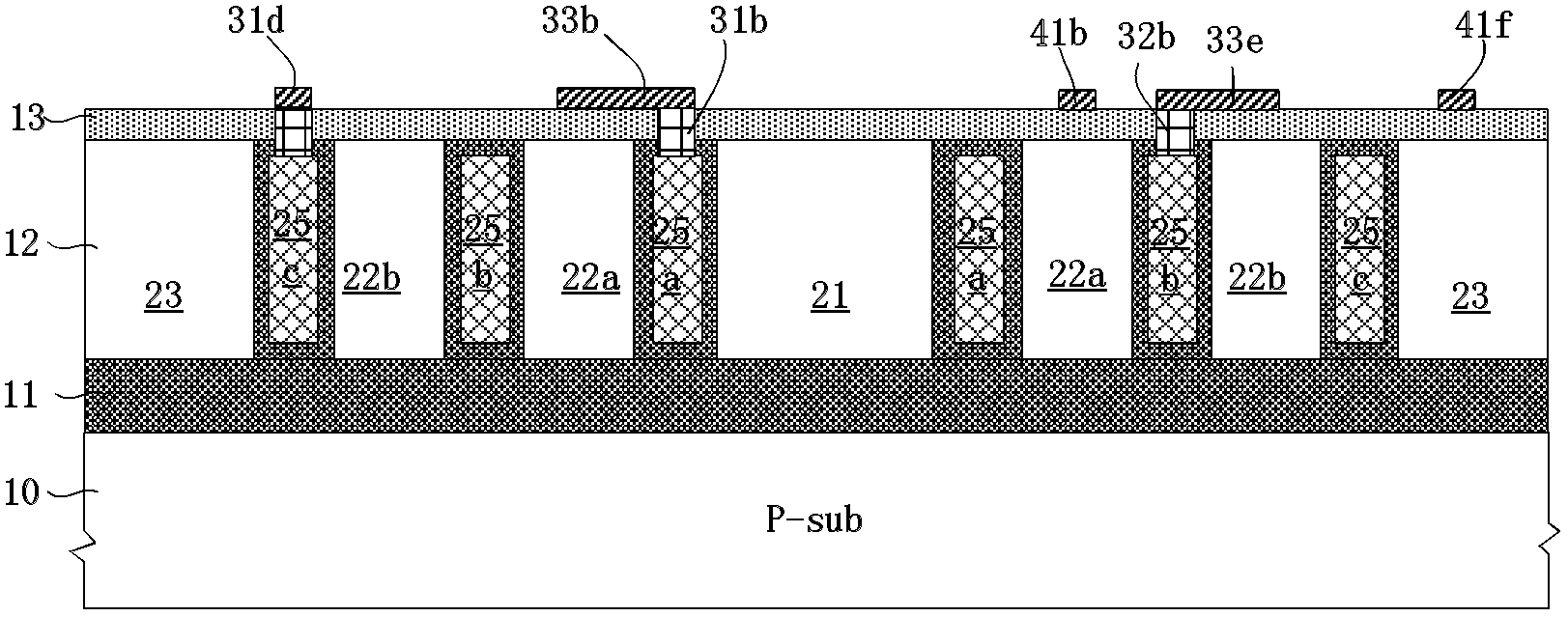

[0023] Embodiment 1 A high-voltage isolation structure based on silicon-on-insulator includes: a P-type substrate 10, a buried oxide layer 11 is provided on the P-type substrate 10, and an N-type epitaxial layer 12 is located above the buried oxide layer 11. The N-type epitaxial layer 12 is provided with a surface passivation layer 13, and the N-type epitaxial layer 12 is provided with a high-voltage circuit area 21 and a low-voltage circuit area 23. The high-voltage circuit area 21 is surrounded by a multi-deep trench isolation structure 50, and the low-voltage circuit area 23 Located outside the multi-deep trench isolation structure 50, the multi-deep trench isolation structure 50 is composed of 2-20 deep trench isolation structures, and a high-resistance polysilicon field plate is provided on the surface passivation layer 13, which is located in the high-voltage circuit area 21 and low-voltage The N-type epitaxial layer of the circuit area 23 is electrically connected to the ...

Embodiment 2

[0031] Embodiment 2 A high-voltage isolation structure based on silicon-on-insulator includes: a P-type substrate 10, a buried oxide layer 11 is provided on the P-type substrate 10, and an N-type epitaxial layer 12 above the buried oxide layer 11, A surface passivation layer 13 is provided on the N-type epitaxial layer 12, a high-resistance polysilicon field plate 41 is provided on the surface passivation layer 13, and a high-voltage circuit area 21 and a low-voltage circuit area 23 are provided in the N-type epitaxial layer 12. The area 21 is surrounded by a three-deep trench isolation structure 50, and the low-voltage circuit area 23 is located outside the three-deep trench isolation structure 50. The three-deep trench isolation structure 50 is composed of a first deep trench isolation structure 50a, a second deep trench isolation structure 50b, and The third deep trench isolation structure 50c is composed of the first deep trench isolation structure 50a adjacent to the high v...

Embodiment 3

[0039] Embodiment 3 Another high-voltage isolation structure based on silicon-on-insulator proposed by the present invention includes: a P-type substrate 10, on which a buried oxide layer 11 is provided, and a N layer above the buried oxide layer 11 Type epitaxial layer 12, a surface passivation layer 13 is provided on the N type epitaxial layer 12, a high resistance polysilicon field plate 42 is provided on the surface passivation layer 13, and a high voltage circuit area 21 and a low voltage The circuit area 23, the high voltage circuit area 21 is surrounded by the double deep groove isolation structure 51, the low voltage circuit area 23 is located outside the double deep groove isolation structure 51, the double deep groove isolation structure 51 is composed of the first deep groove isolation structure 51a, the second The deep trench isolation structure 51b is composed of the first deep trench isolation structure 51a adjacent to the high voltage circuit area 21, the second d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More