Manufacturing method of semiconductor device

A manufacturing method and semiconductor technology, applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of increased design pattern density, micro-loading effect, and decreased etching rate, so as to improve etching efficiency, reduce The effect of the micro-loading effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] In the following description, numerous specific details are set forth in order to provide a more thorough understanding of the present invention. It will be apparent, however, to one skilled in the art that the present invention may be practiced without one or more of these details. In other instances, some technical features known in the art have not been described in order to avoid obscuring the present invention.

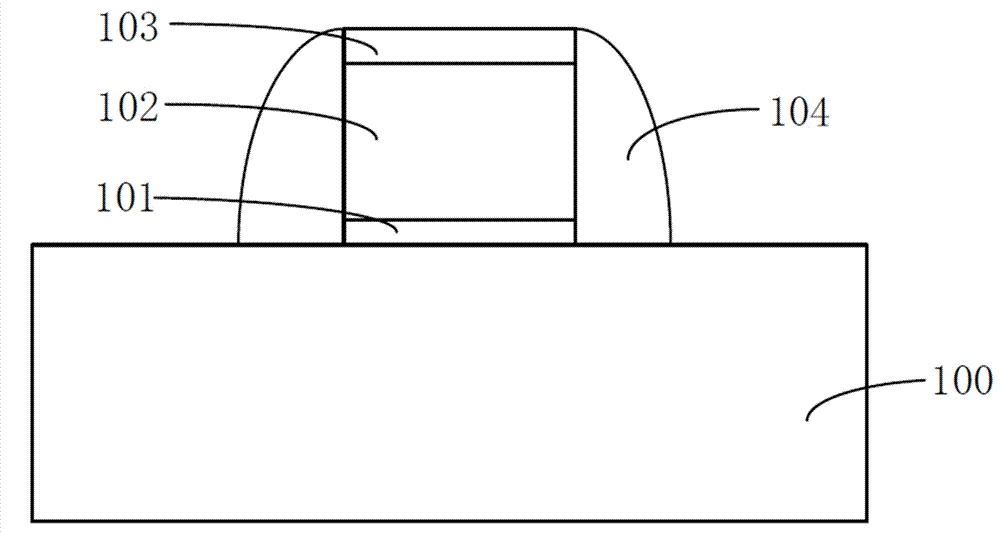

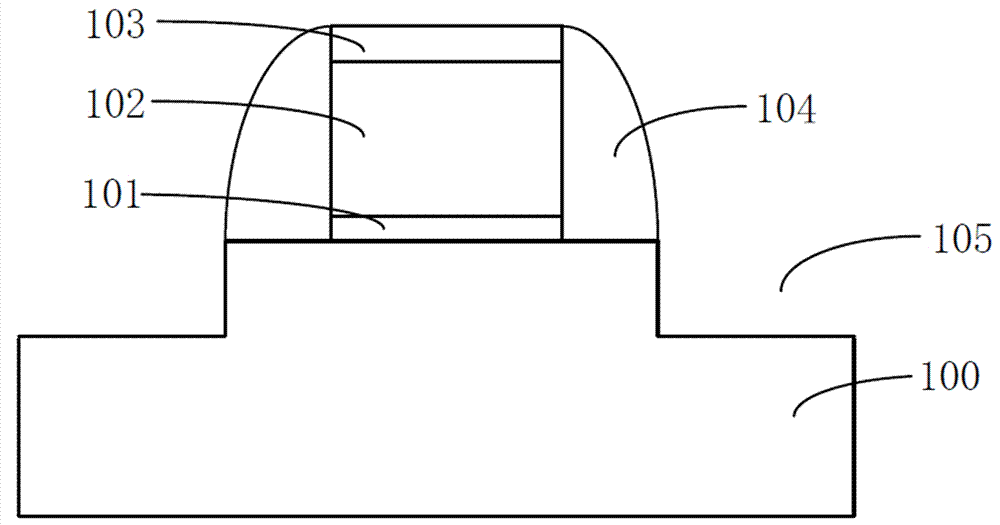

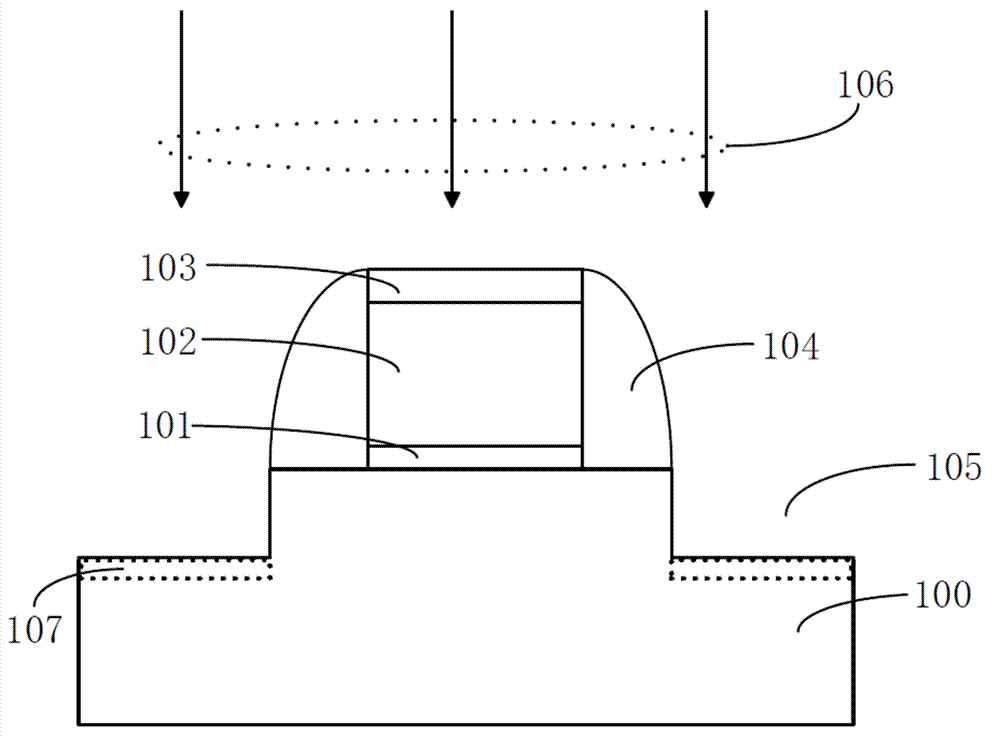

[0025] In order to thoroughly understand the present invention, detailed steps will be presented in the following description to explain how the present invention forms a Σ-shaped groove for embedded SiGe strained MOS devices. Obviously, the practice of the present invention is not limited to the specific details familiar to those skilled in the semiconductor arts. Preferred embodiments of the present invention are described in detail below, however, the present invention may have other embodiments in addition to these detailed descriptions.

[0026] It ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More