Printed circuit board (PCB) signal group delay analysis system and method

A printed circuit board and delay analysis technology, which is applied in the direction of electronic circuit testing, electrical digital data processing, special data processing applications, etc., can solve problems such as impossibility, frequency problems, system operation failure, etc., and achieve the effect of correct timing relationship

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

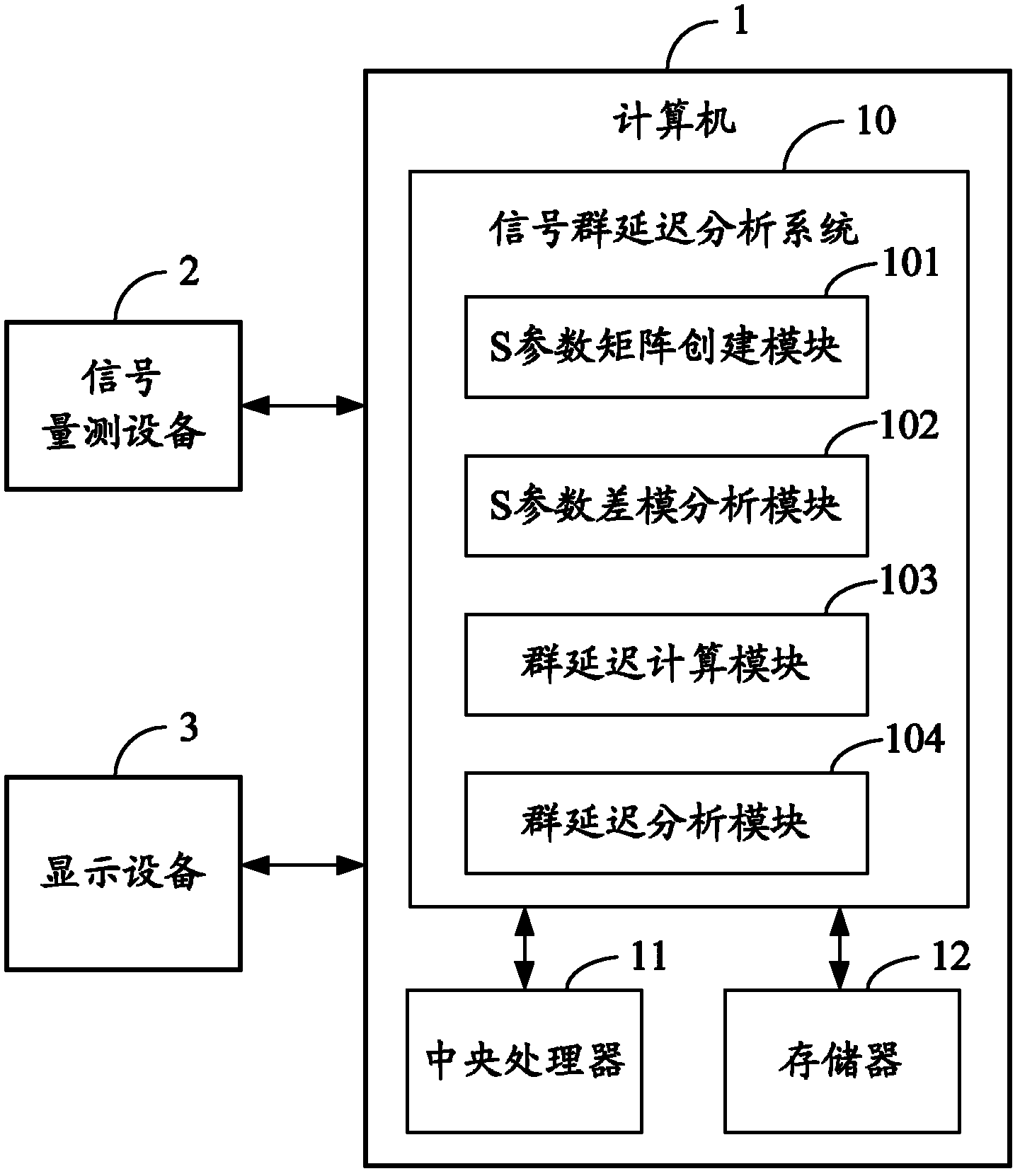

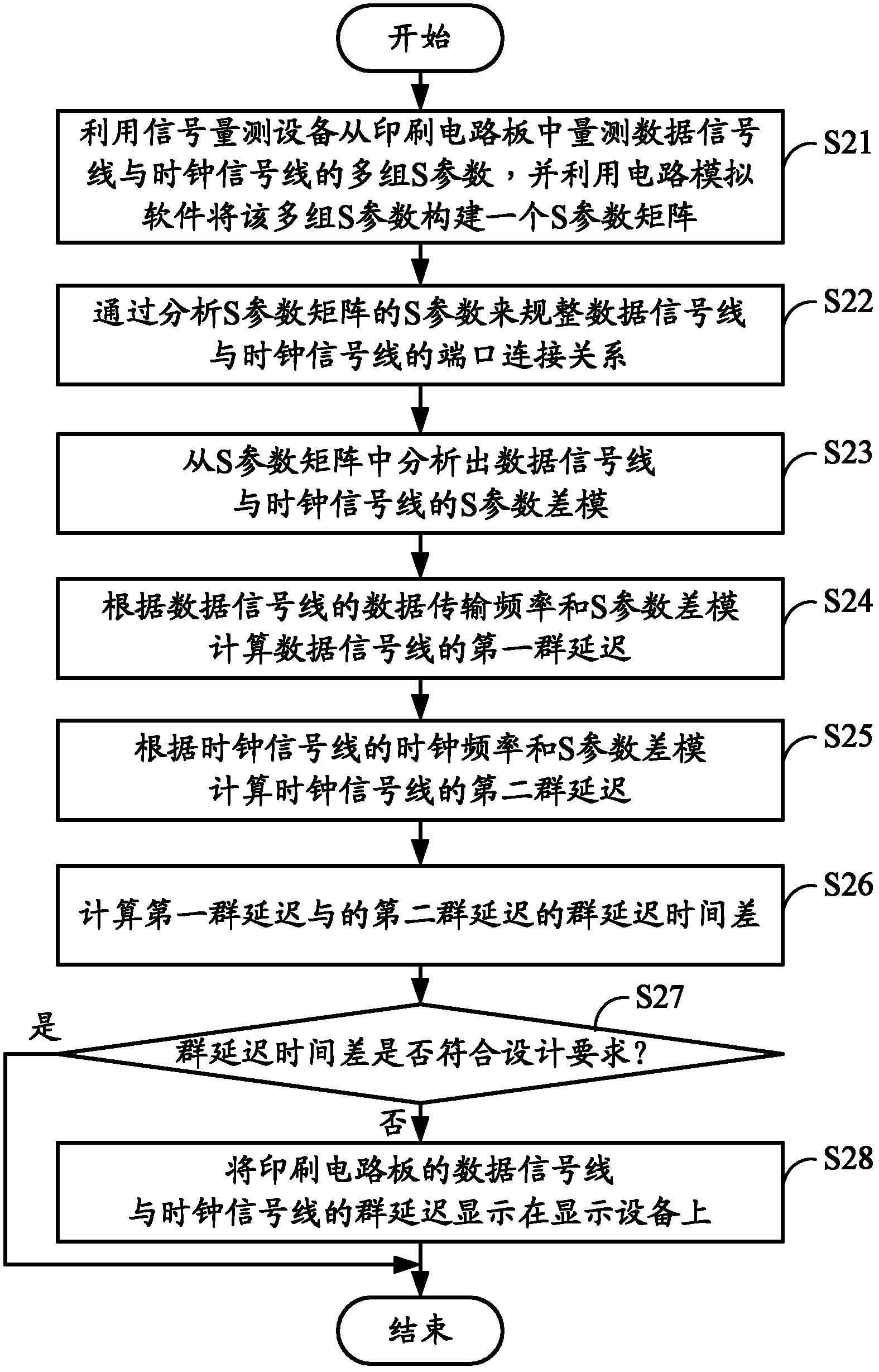

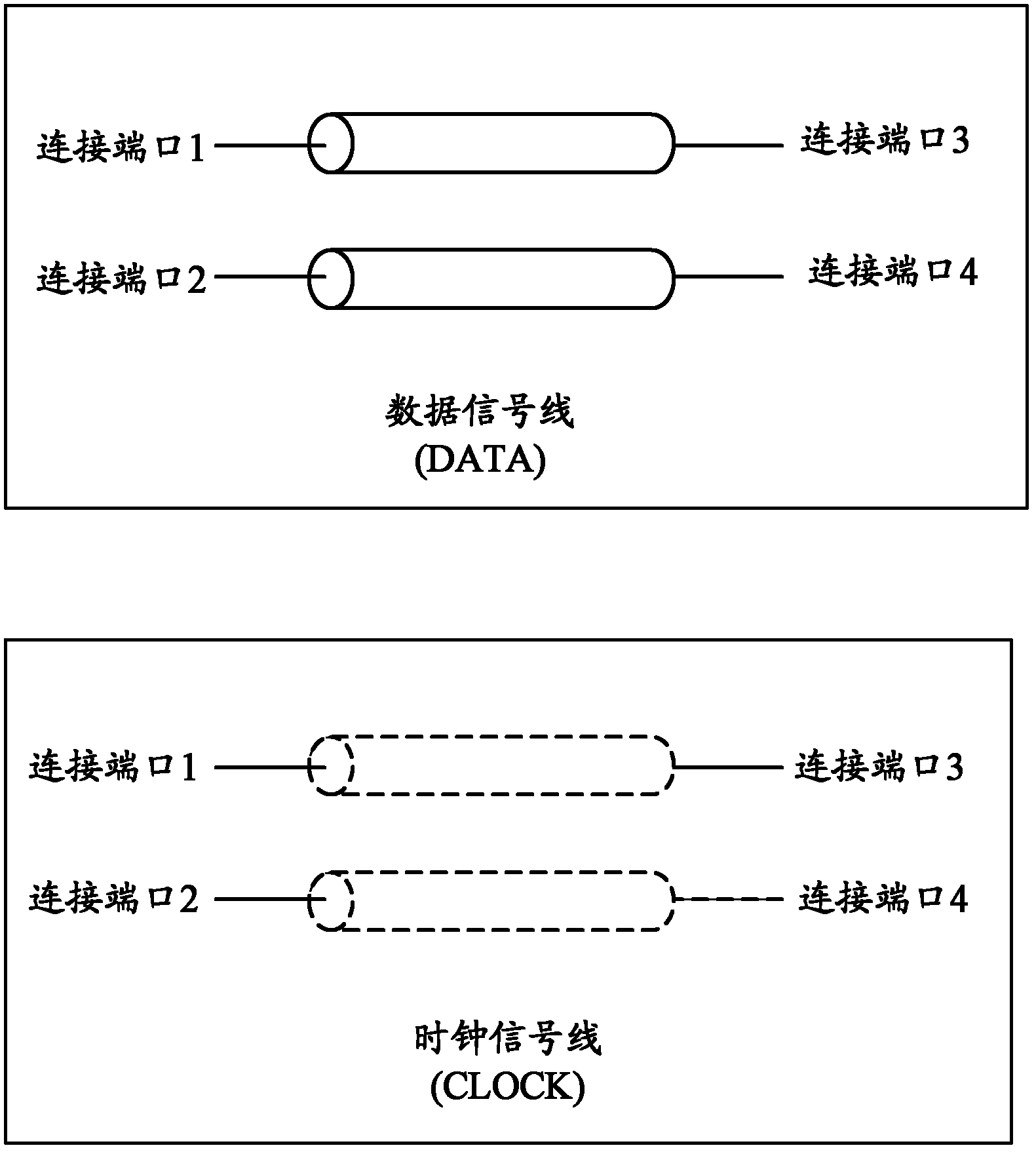

[0023] Such as figure 1 Shown is a structure diagram of a preferred embodiment of the system 10 for analyzing the signal group delay of the printed circuit board of the present invention. The printed circuit board (Printed Circuit Board, PCB) includes, but is not limited to, the circuit boards of computer motherboards, game machines, and household appliances. The signal group delay (Signal Group Delay) is defined as the delay time of each signal corresponding to each frequency, which is represented by the slope change of the signal transmission channel phase versus frequency. In this embodiment, the signal transmission channel includes a data (DATA) signal line and a frequency (CLOCK) signal line, refer to image 3 As shown, when wiring a printed circuit board, there may be multiple sets of data signal lines, but generally there is only one set of clock signal lines. The data signal line is used for data transmission between electronic components in the printed circuit board...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap