Hierarchical structure focused on high performance SRAM (Static Random Access Memory)

A hierarchical structure, high-performance technology, applied in the direction of information storage, static memory, digital memory information, etc., can solve the problem of no increase in throughput, achieve the effect of reducing delay, avoiding delay short-board problems, and optimizing performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

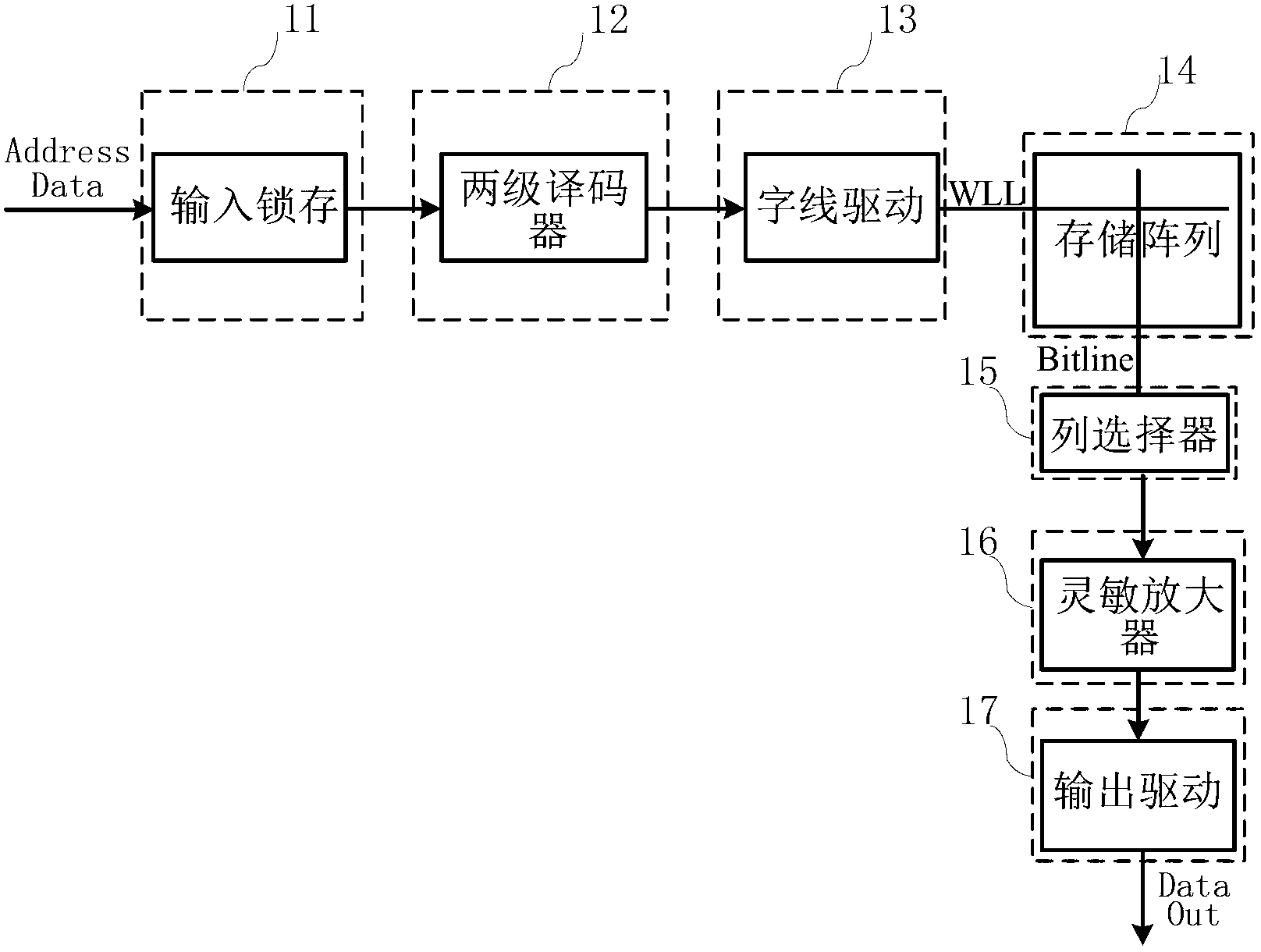

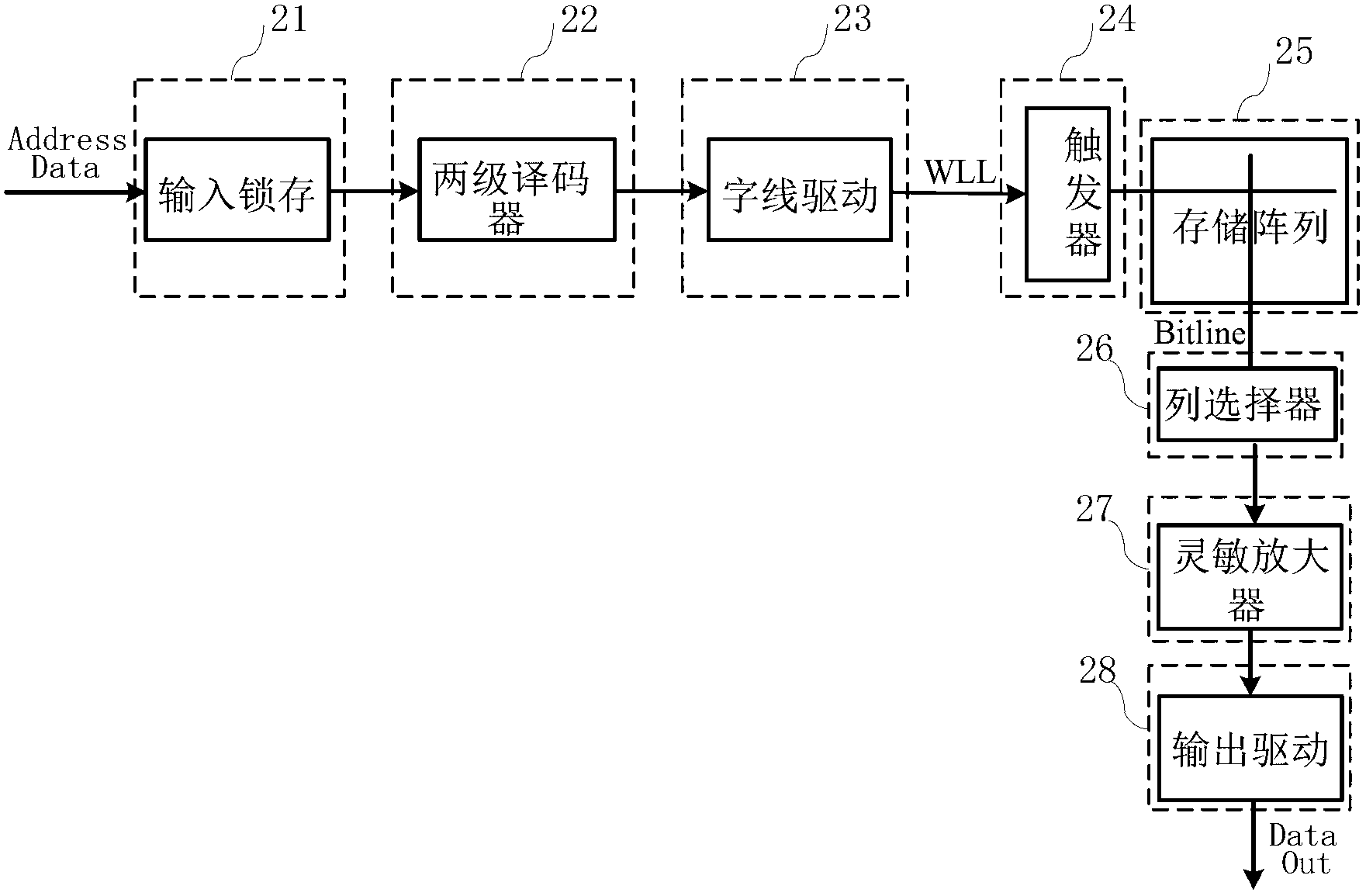

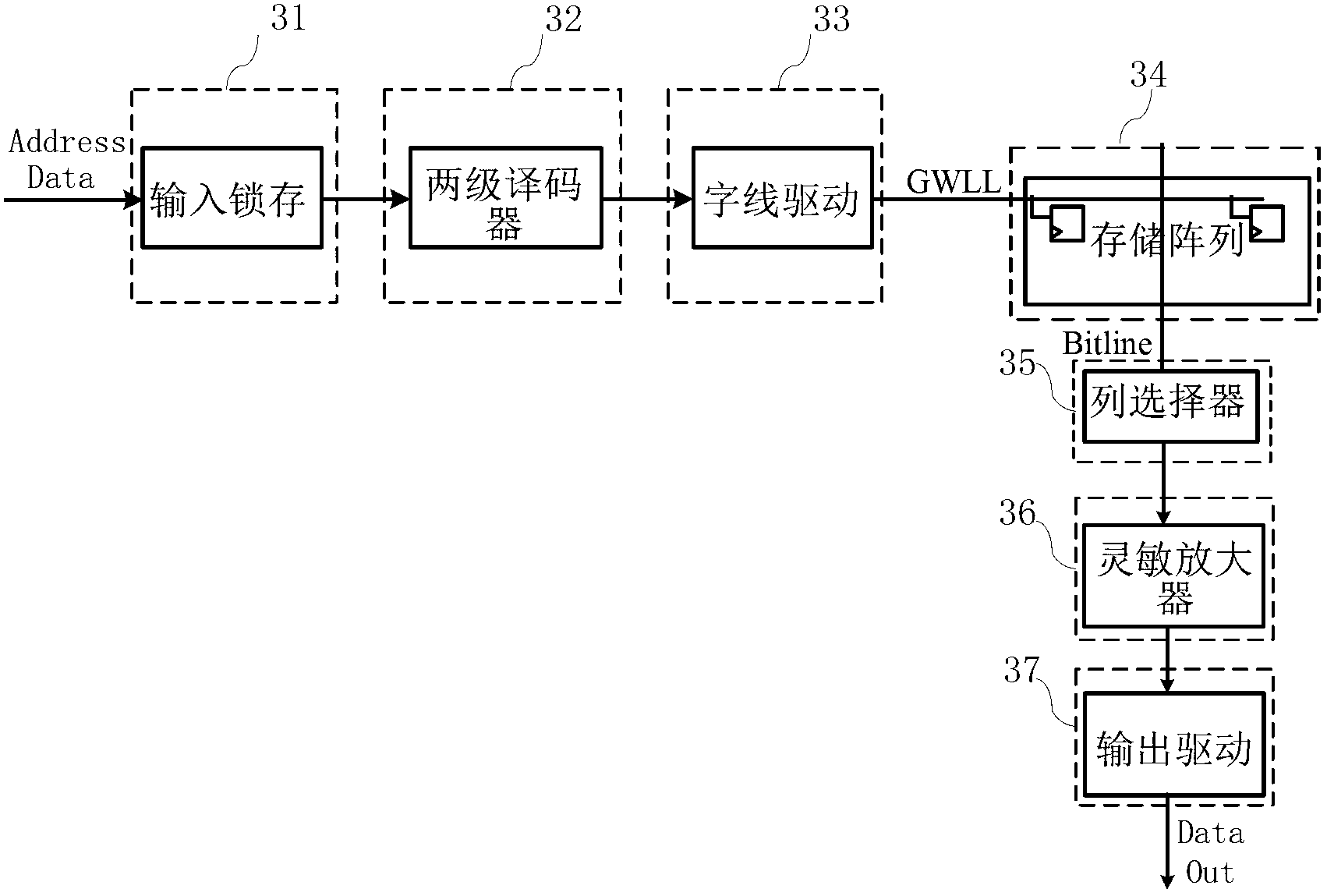

[0017] As a device that directly exchanges data with the CPU in a computer system, SRAM must meet the performance requirements of high operating frequency and low delay. The high-performance SRAM architecture and the optimization of the critical path proposed by the present invention can effectively reduce the delay and increase the working frequency, thereby realizing the optimization of the SRAM performance.

[0018] SRAM is mainly composed of modules such as decoder, array read and write, and timing control. Traditional structure signal flow from decoder, array read and write to final output. Due to the limitation of area efficiency, it is difficult to control the delay of reading and writing of the decoder and array within 200ps. In order to achieve an operating frequency above 4GHz, the traditional structure is limited.

[0019] In order to illustrate the improvement of SRAM performance brought by high-performance SRAM architecture and critical path optimization, we anal...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More