Method for detecting faults of integrated circuit

An integrated circuit and fault detection technology, applied in the direction of electronic circuit testing, etc., can solve the problems of discount of practical effect, limited number of detectable nodes, noise, etc., and achieve the effect of insensitivity to noise.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

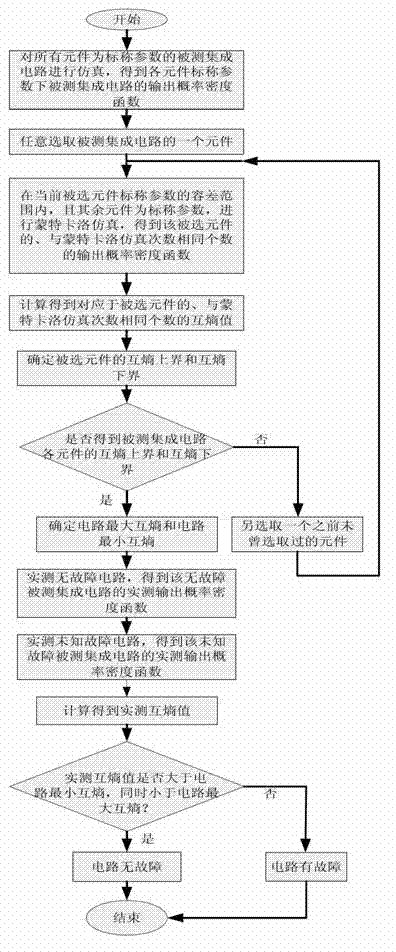

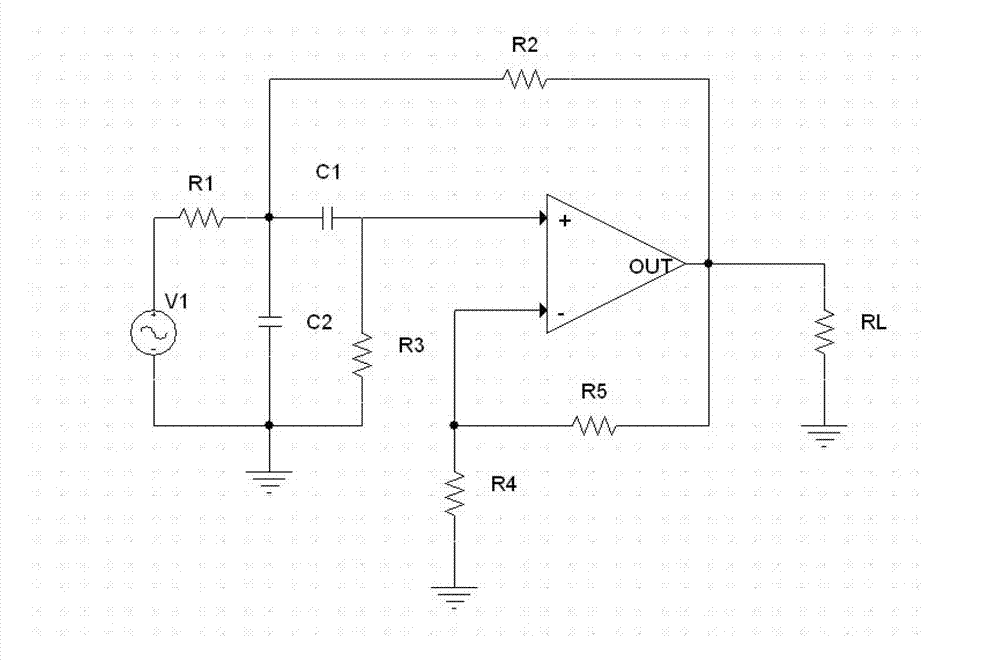

[0070] Such as figure 1 , figure 2 shown. The second-order Sallenkey band-pass filter in the international standard circuit is selected to verify the integrated circuit fault detection method of the present invention. The nominal parameters of each component of the second-order Sallenkey bandpass filter are: R1=5.18 KΩ, R2=1 KΩ, R3=2 KΩ, R4= R5=4 KΩ, RL=10 KΩ, C1=C2=5nF. The tolerance range of each component of the second-order Sallenkey bandpass filter circuit is ±5%; use "↑" and "↓" to represent the positive offset and negative offset of the component parameters of the second-order Sallenkey bandpass filter, respectively. For example, "Rx 10%↑" means that the resistance value of resistor Rx is positively shifted by 10%, such as "Cy 10%↓" means that the capacitance value of capacitor Cy is negatively shifted by 10%. The automatic regression model of the second-order Sallenkey bandpass filter is adopted, and the order of the AR model is 10, that is, q=10. The number of ou...

Embodiment 2

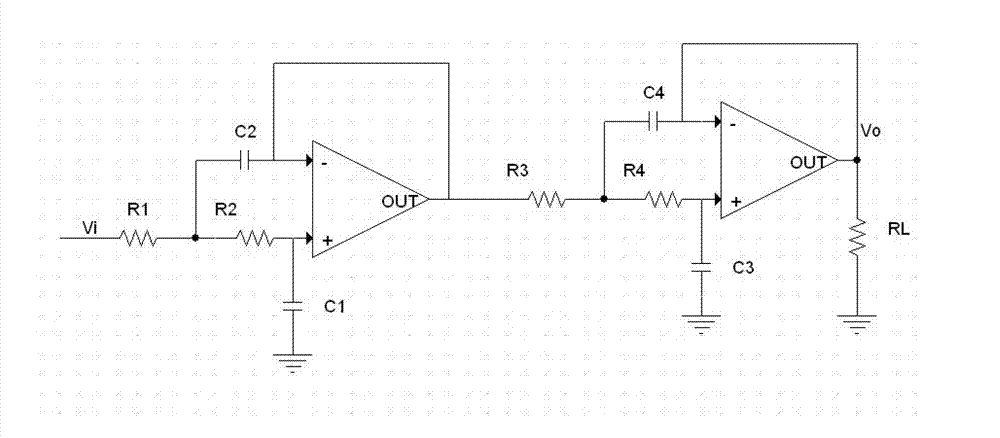

[0086] Such as figure 1 , image 3 shown. The same places as in Embodiment 1 will not be described again, the difference is that a fourth-order low-pass Chebyshev filter in an international standard circuit is selected to verify the method of the present invention. The nominal parameters of each component of the fourth-order low-pass Chebyshev filter are: R1=26.7 KΩ, R2=73 KΩ, R3=11.8 KΩ, R4=67.8 KΩ, RL=10 KΩ, C1=4.7 nF, C2= 10nF, C3=1nF, C4=47nF. The upper bounds and lower bounds of the cross-entropy of each element of the fourth-order low-pass Chebyshev filter within the tolerance range of ±5% are shown in the table below. It can be seen from the table below that the minimum cross-entropy of the circuit of the fourth-order low-pass Chebyshev filter is -0.1596, and the maximum cross-entropy of the circuit is 0.1701.

[0087]

[0088] Put "R1 9%↑", "R3 20%↑", "R1 7%↓", "R3 10%↓", "C2 10%↓", "R1 8%↓", "C1 8%↓" The seven faults are respectively injected into the fourth-o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More