Method for manufacturing inverted LED chip

An LED chip and manufacturing method technology, which is applied to electrical components, circuits, semiconductor devices, etc., can solve problems such as affecting the luminous efficiency of the LED chip, the N-level solder layer 38 is too long, and affecting the packaging quality rate, etc., so as to avoid electrode soldering. Or desoldering, increasing the area of the light-emitting area, and improving the effect of the good rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

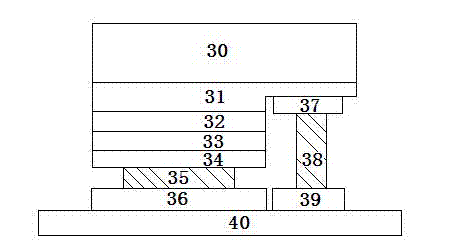

[0070] Combine below Figure 2 to Figure 18 , the present invention is further described:

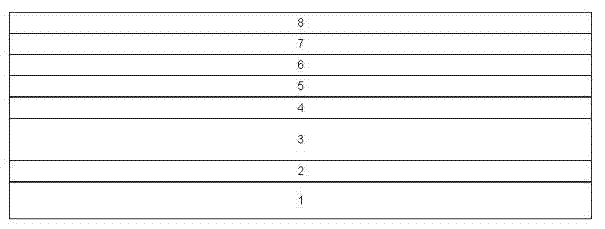

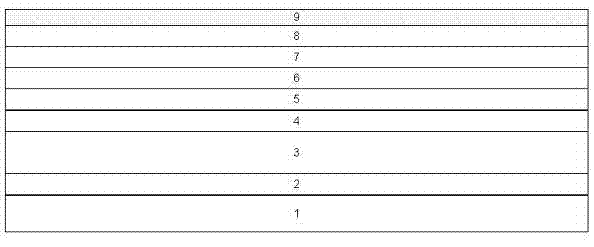

[0071] Such as figure 2 As shown, the substrate 1 is a carrier, generally made of materials such as sapphire, silicon carbide or GaN. Buffer layer 2 is a transitional layer on which high-quality N, P, quantum wells and other materials are grown. LED is composed of pn structure, buffer layer 2, N-type layer 3 layers, N-type confinement layer 4, P-type confinement layer 6 and P-type layer 7 are to form P and N-type materials required for making LED. The active region layer 5 is the light-emitting region of the LED, and the color of the light is determined by the structure of the active region. P-type ohmic contact layer 8 is the last layer of material growth, and the carrier doping concentration of this layer is relatively high, the purpose is to make smaller ohmic contact resistance. The P-type metal ohmic contact layer is not formed by growth, but by evaporation or sputtering. One ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More