Formalization method for verification and performance analysis of high reliable communication system

A formal method and communication system technology, applied in the field of formalization for verification and performance analysis of highly reliable communication systems, can solve problems such as state explosion, low abstraction level, and too many states

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

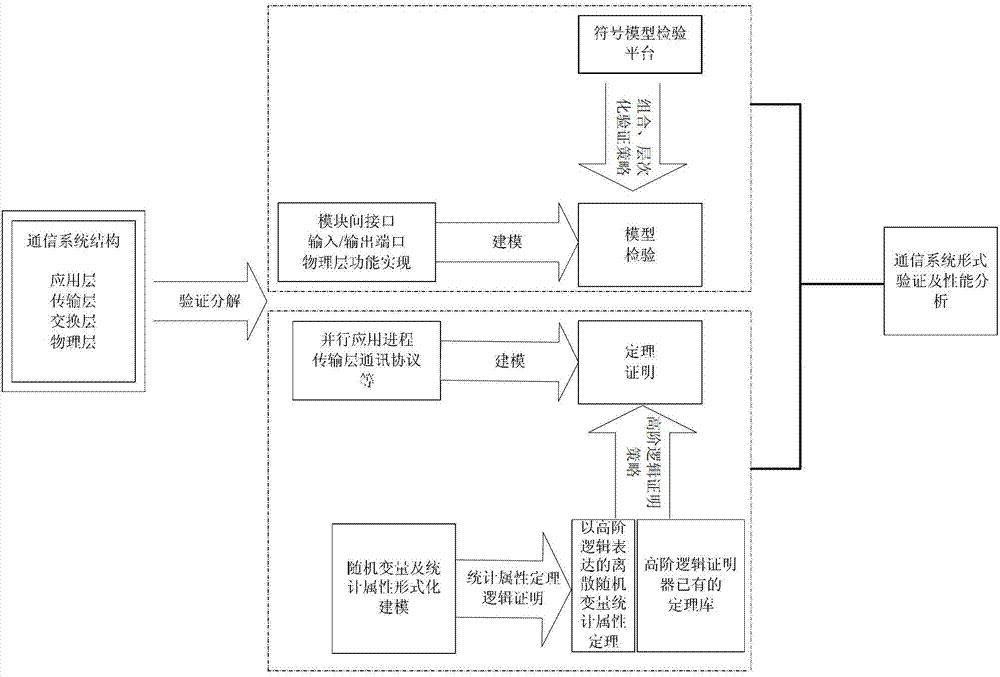

[0019] In order to make the features and advantages of the present invention more clearly understood, below in conjunction with accompanying drawing, describe in detail as follows: figure 1 The overall architecture realized by the present invention is described.

[0020] When SOC designers verify the behavior and function correctness of the designed or implemented on-chip communication system, a formal verification method of the present invention can realize the attribute verification of the system at different levels of abstraction and based on the established formal model, carry out Performance analysis:

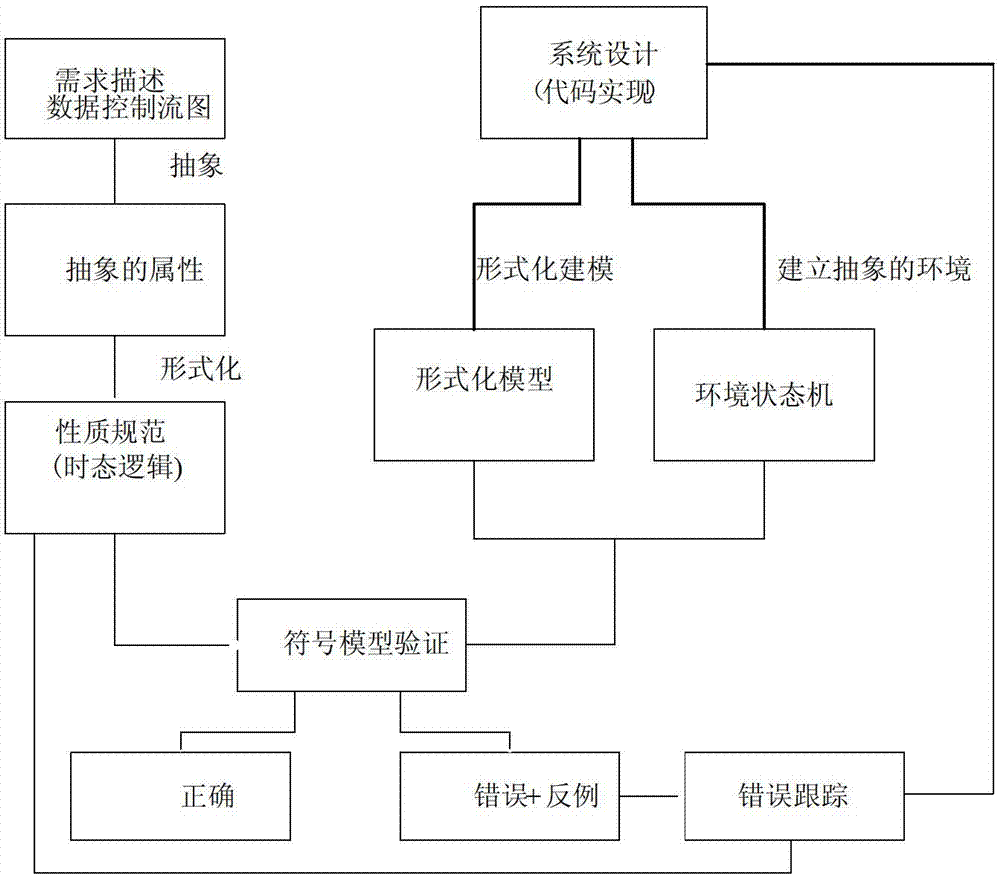

[0021] See figure 2 , the present invention is a formalized verification method for performance inspection and analysis of high-reliability communication systems, and its specific implementation steps are:

[0022] Step 1: Analyze the system design and perform verification decomposition. Such as figure 2 As shown, according to the system function and realization char...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More