A memory data buffering method and device

A technology of memory data and buffering method, applied in the computer field, can solve problems such as slow memory reading speed, affecting request cache response time, etc., to achieve the effect of increasing data cache, reducing times, and reducing delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0077] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

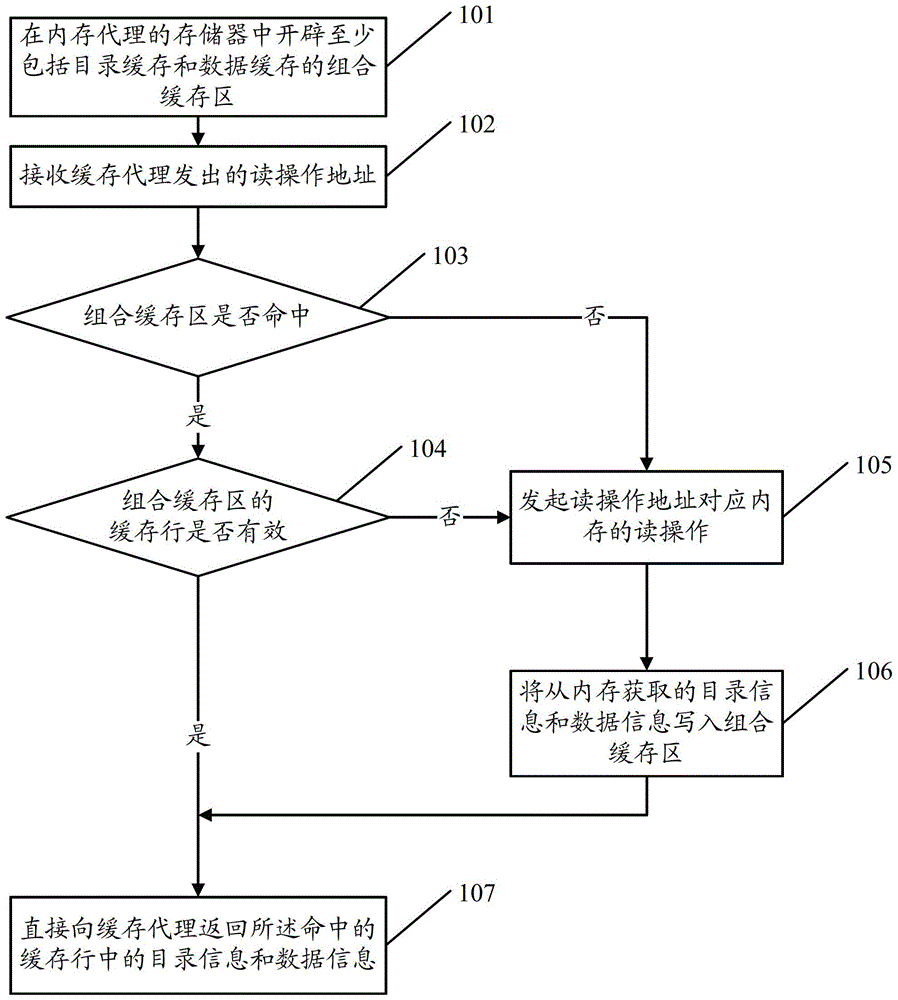

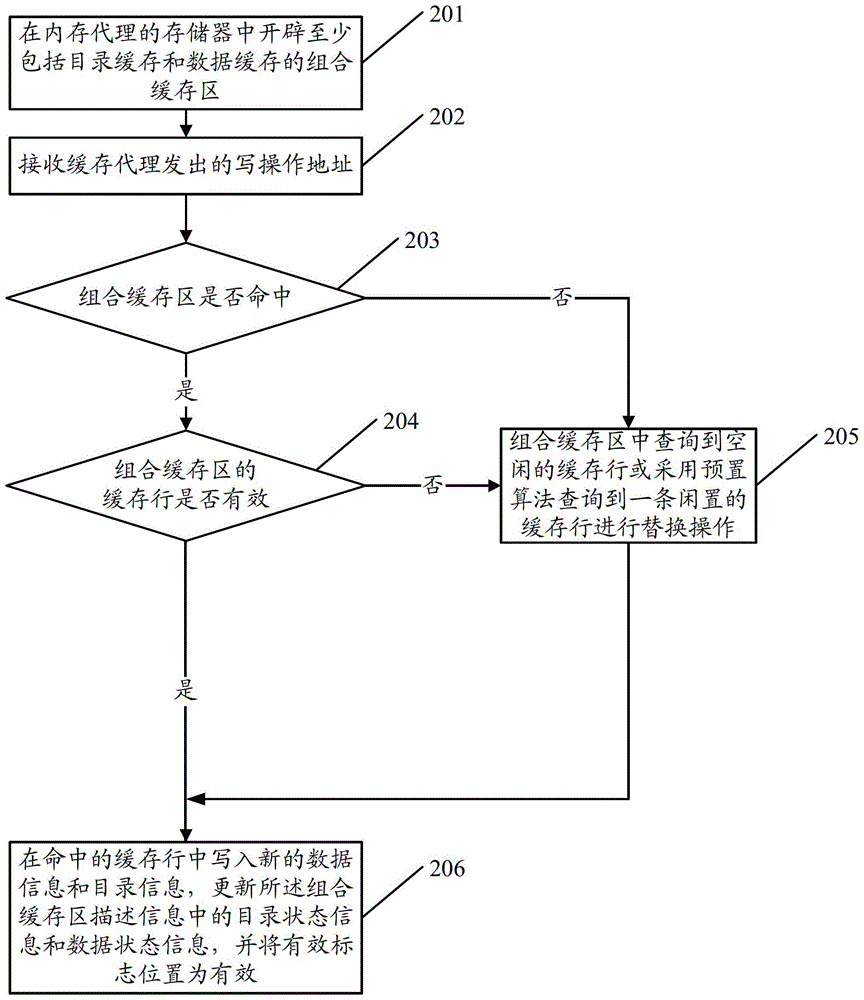

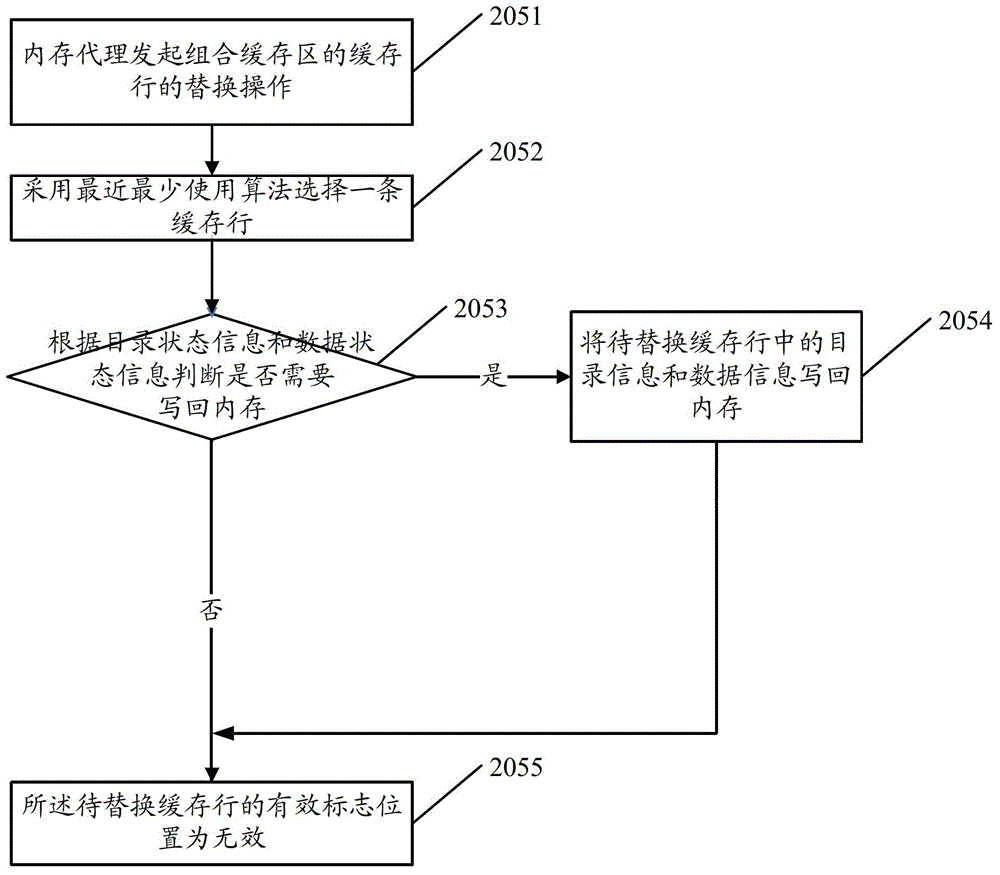

[0078] see figure 1 , which is a schematic flow chart of a first memory data buffering method according to an embodiment of the present invention, and the process includes:

[0079] Step 101, open up a combined cache area including at least a directory cache and a data cache in the memory of the memory agent.

[0080] Specifically, the directory cache is a copy of the directory information memory line loaded into the memory agent in the memory. The state informati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More