A communication acceleration method for smart substation terminal equipment chips

A technology for smart substations and terminal equipment, applied in electrical components, electrical digital data processing, instruments, etc., can solve problems such as low CPU operating efficiency, achieve complex tasks, reduce workload, and increase processing delays

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

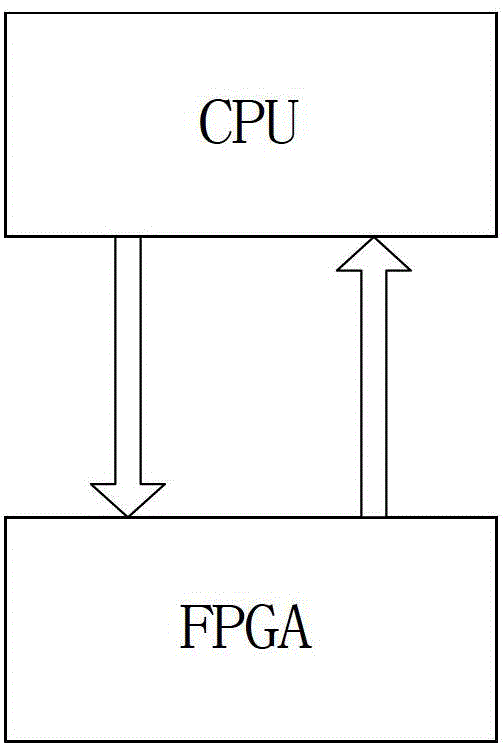

[0031] A method for accelerating communication between chips of smart substation terminal equipment includes the following steps:

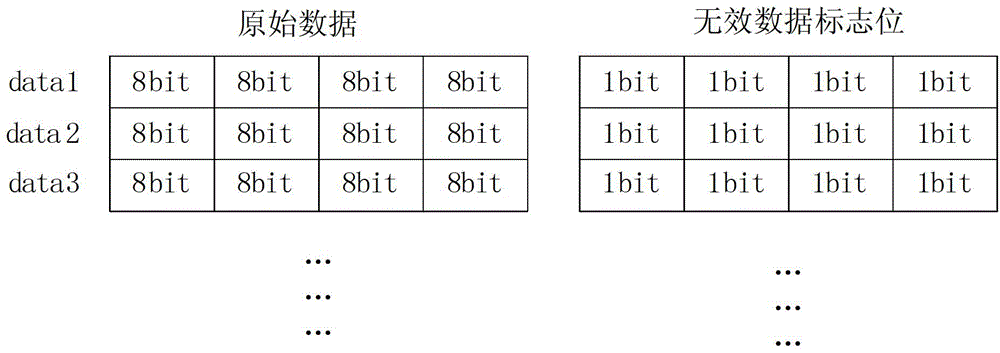

[0032] Step 1: The network interface CPU of the smart substation terminal device generates an invalid data flag according to the data characteristics of the message. The invalid data flag is assigned a value to distinguish whether the corresponding data needs to be sent. Preferably, the invalid data flag is 0 ,1 distinguishes whether it is valid, for example, 0 can be used to indicate invalid flag bit, and 1 can be used to indicate valid flag bit. It is judged from the high bit of the 32bit of the data whether or not the data needs to be sent. It is set to an invalid flag.

[0033] In this embodiment, the data is processed as a whole, and invalid data flags are sequentially generated for all data that needs to be sent: generation method: start from the high bit of 32bit to determine whether the data needs to be sent, and if you need to send the flag T...

Embodiment approach 2

[0040] A method for accelerating communication between chips of smart substation terminal equipment includes the following steps:

[0041] Data is processed in blocks, and the implementation method is as follows:

[0042] (1) Divide the data into blocks, according to the different functions of the data, or different sending targets, etc., all the data that the CPU needs to send to the FPGA can be divided into blocks;

[0043] (2) For the data that needs to be sent for each data block, generate invalid data flags in sequence;

[0044] Generation method: start from the high bit of 32bit to determine whether the data needs to be sent, if it needs to be sent, the position of the flag is set to a valid flag bit, otherwise, it is set to an invalid flag bit. The method of judging valid or invalid is determined by the data characteristics of the CPU;

[0045] (3) For each data block, combine the invalid data flags into 8-bit data;

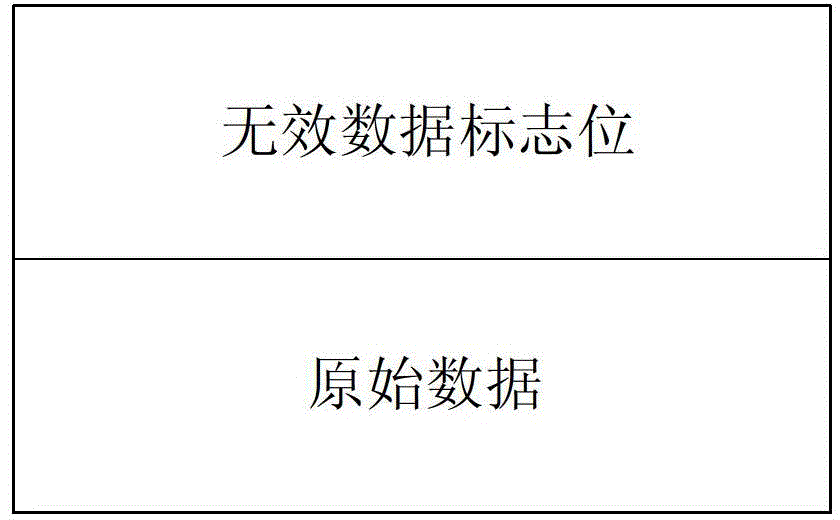

[0046] (4) Arrange the combined invalid data flag data with th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More