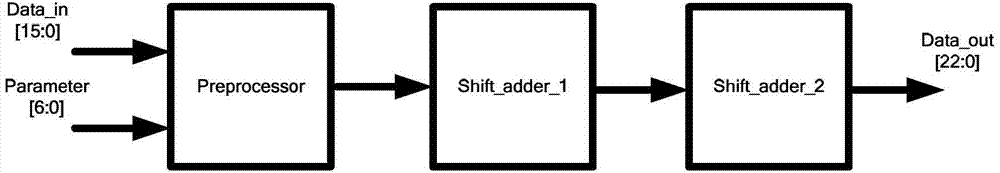

Multiplying unit structure for discrete cosine transformation (DCT)/inverse discrete cosine transformation (IDCT) circuit under high efficiency video coding (HEVC) standard

A technology of multipliers and circuits, which is applied in calculations using number system representations and calculations using non-contact manufacturing equipment, etc., can solve the problems of large computing resource occupation and long computing time, and reduce power consumption and chip area. The effect of improving computing speed and streamlining hardware resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

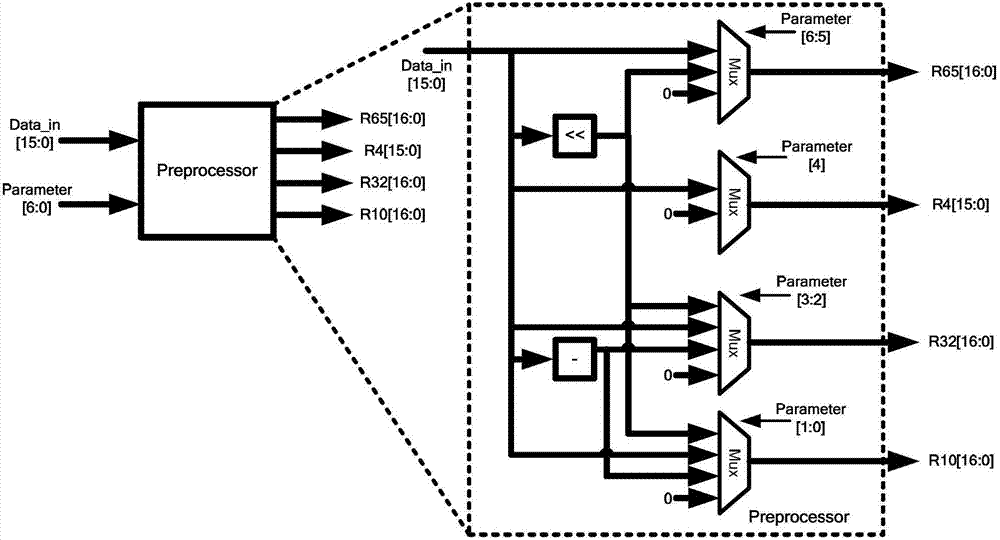

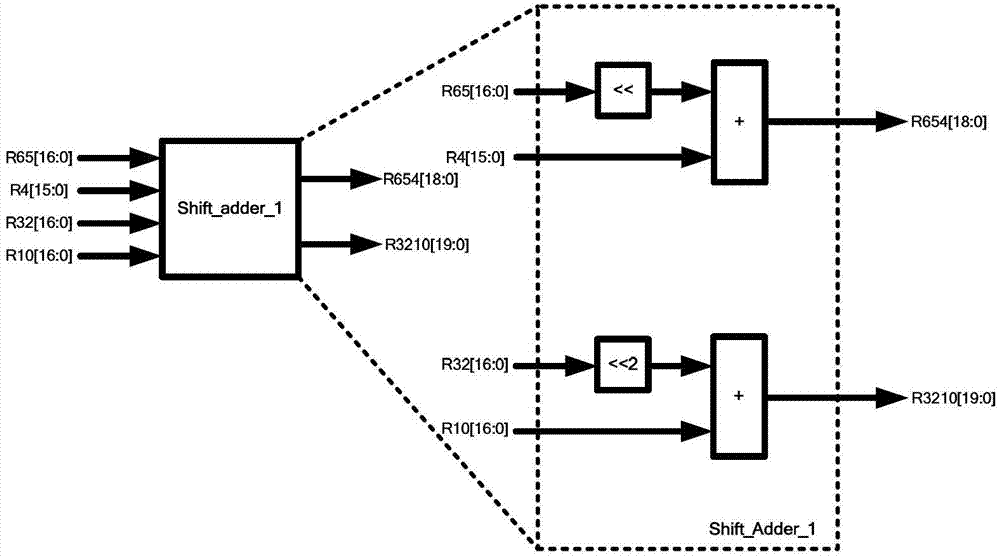

[0053] 1) Usually, the multiplier for realizing constant multiplication operation can be realized by shift-add operation, so the shift-add circuit design is the basis of the present invention. The shift-and-add algorithm of general integer multiplication is realized by the method of unit shift-add. The constant multiplication parameter used by DCT / IDCT is a 7-bit integer, which is applied to the general shift-add circuit structure, using 6 shift operations and 6 According to the usual design principles, it is estimated that a shift and an addition take one cycle for one addition operation, and a general shift and addition circuit needs to take at least 6 cycles to complete the operation. In the circuit design method, such an algorithm has disadvantages such as a long operation time and a large occupation of operation resources.

[0054] 2) By studying the constant multiplication operation process used by DCT / IDCT, analyzing the characteristics of the constant value used in the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com