Two-port static random access memory using single-port memory unit

A memory cell, static random technology, applied in static memory, digital memory information, information storage and other directions, can solve the problems of increasing word line delay, increasing word line delay, increasing read access time, etc., and achieves area reduction and reduction. area effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] Embodiments of the present invention will be further described below in conjunction with the accompanying drawings.

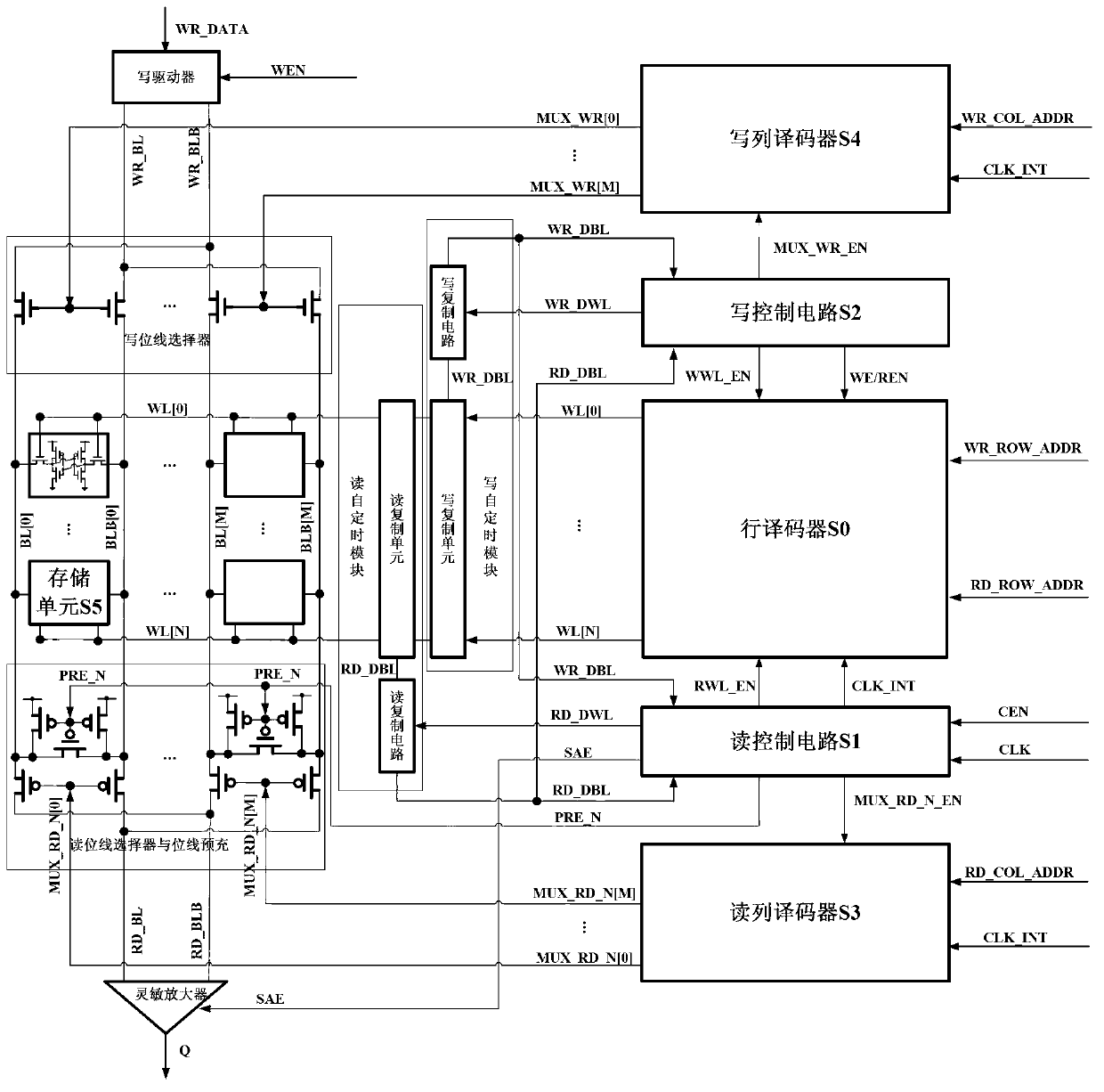

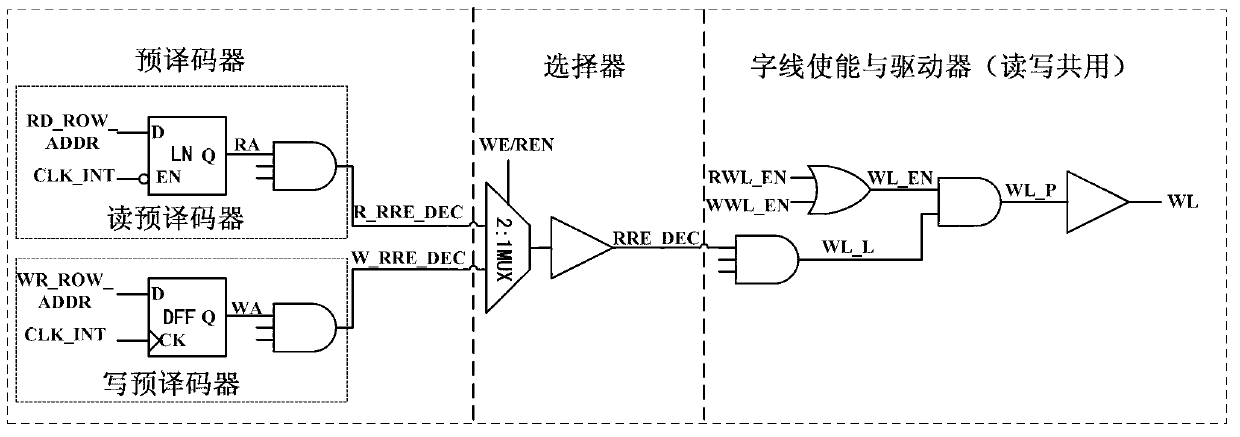

[0027] see figure 1 As shown, the present invention uses a two-port SRAM diagram of a single-port memory unit, including a memory cell array, a row decoder S0, a read column decoder S3, a read control circuit S1, a write column decoder S4, Write control circuit S2, write driver, write bit line selector array, write self-timer module, read bit line selector and bit line prefill array, sense amplifier and read self-timer module.

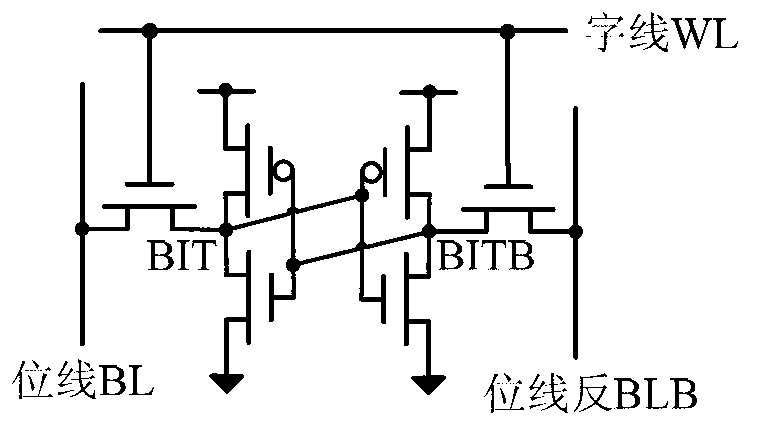

[0028] The write bit line selector array includes multiple write bit line selectors, and each write bit line selector is connected to a corresponding row of memory cells through a pair of bit lines BL / BLB. The array of read bit line selectors and bit line precharges includes multiple read bit line selectors and bit line precharges, each of which is connected to a corresponding row of memory cells through a pair of bit lines BL / B...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com