Semiconductor device and operating method thereof

A technology for semiconductors and devices, applied in the field of internal voltage generating circuits, can solve the problems of reduced response speed of internal voltage generating circuits, increased current usage of semiconductor devices, and deterioration of semiconductor device performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

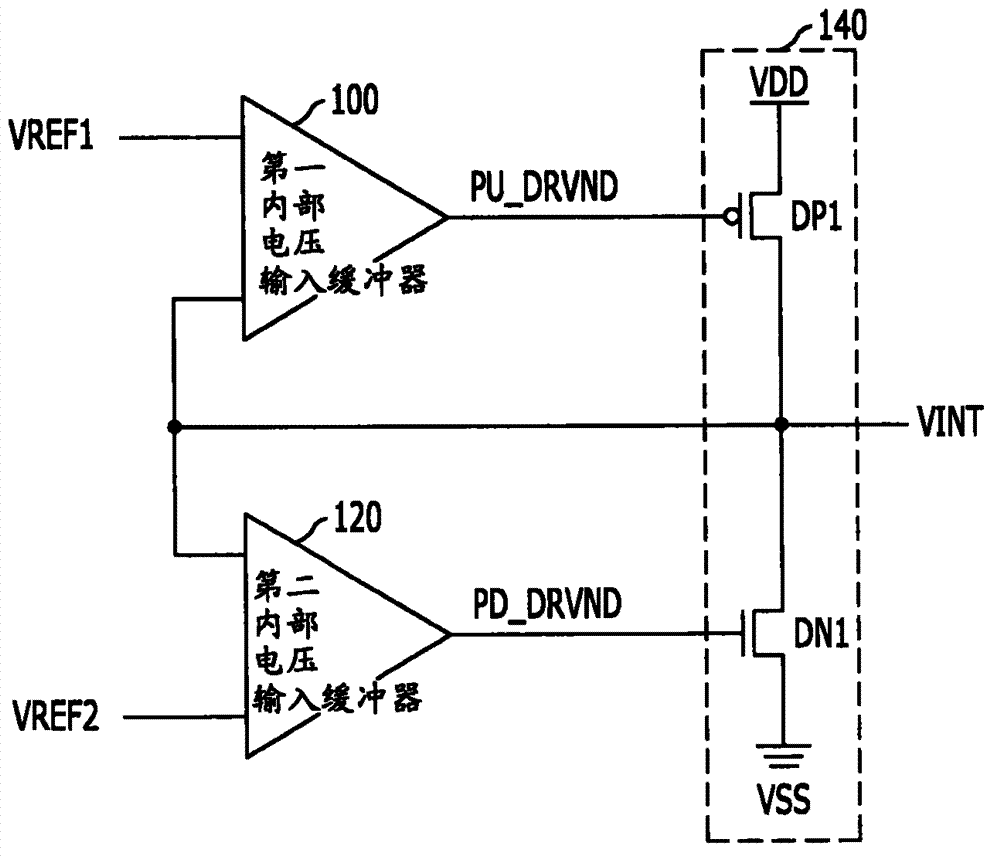

[0037] Figure 3A with Figure 3B is a circuit diagram illustrating an internal voltage generating circuit of the semiconductor device according to the first embodiment of the present invention.

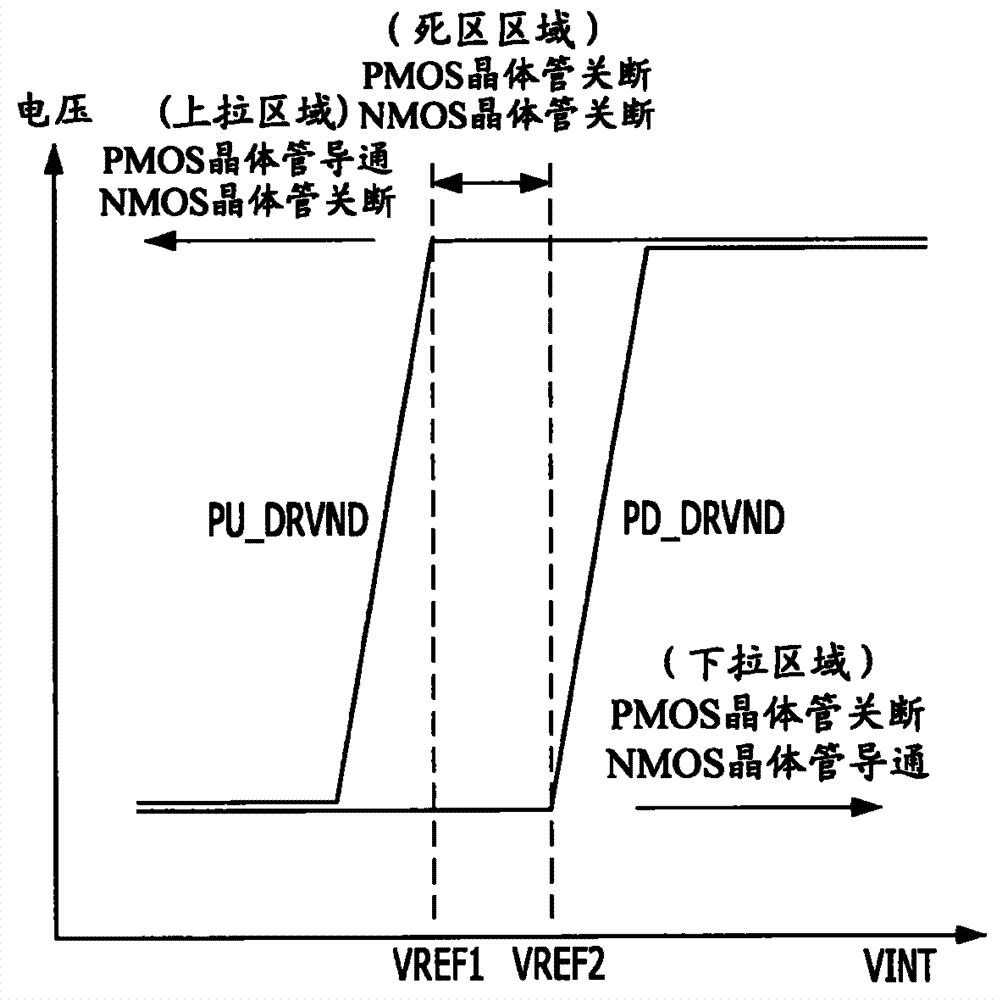

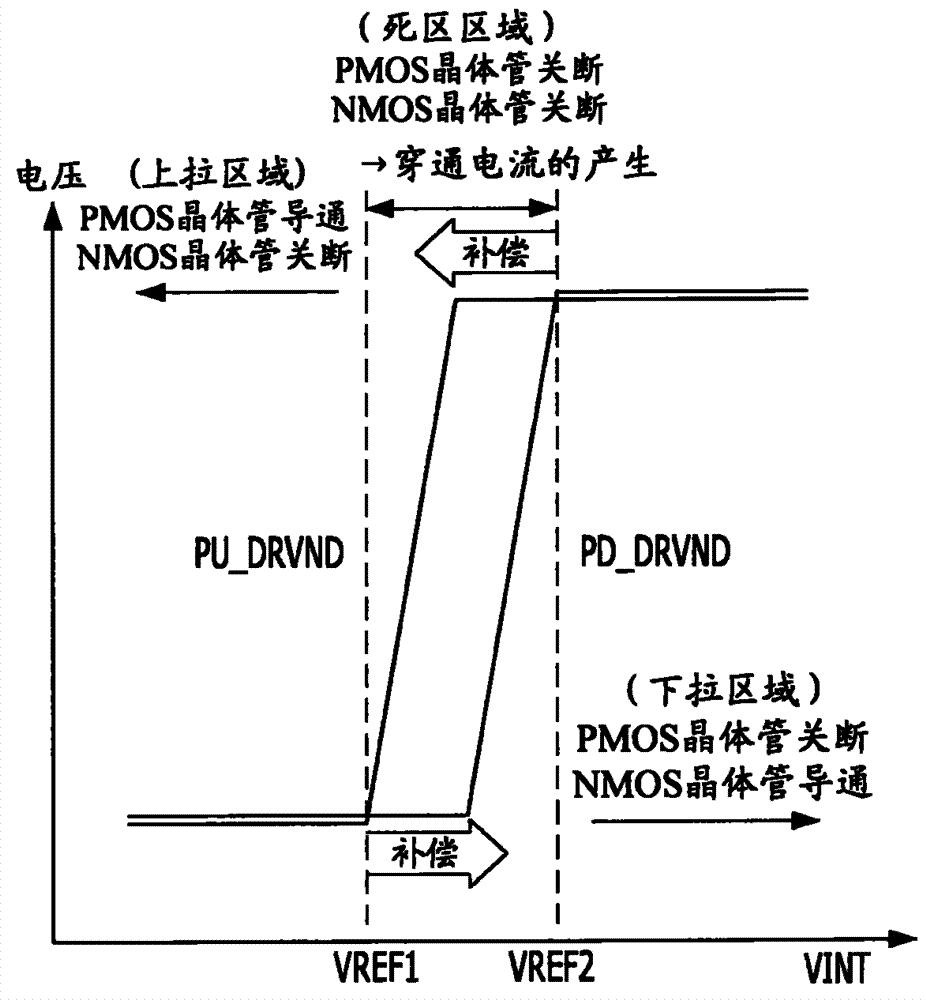

[0038] Figure 4 is description Figure 3A with Figure 3B A graph showing the operation of the internal voltage generating circuit of the semiconductor device according to the first embodiment of the present invention.

[0039] see Figure 3A , The internal voltage generating circuit of the semiconductor device according to the first embodiment of the present invention includes an internal voltage input buffer 300 , an internal voltage driving module 340 , a current supplying module 360 and a current sinking module 370 . The internal voltage input buffer 300 includes a voltage detection unit 302 and a driving node level determination unit 304 . The driving node level determination unit 304 includes a supply current source 3042 , a sink current source 3044 and a floating curr...

no. 2 example

[0093] Figure 5A with Figure 5B is a circuit diagram illustrating an internal voltage generating circuit of a semiconductor device according to a second embodiment of the present invention.

[0094] Image 6 Is the explanation based on Figure 5A with Figure 5B A graph showing the operation of the internal voltage generating circuit of the semiconductor device of the second embodiment of the present invention.

[0095] see Figure 5A , the internal voltage generating circuit of the semiconductor device according to the second embodiment of the present invention includes a first internal voltage input buffer 500, a second internal voltage input buffer 560, a third internal voltage input buffer 570, and an internal voltage driving module 540A and 540B. The first internal voltage input buffer 500 includes a voltage detection unit 502 and a driving node level determination unit 504 . The driving node level determination unit 504 is configured to include a supply current ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com