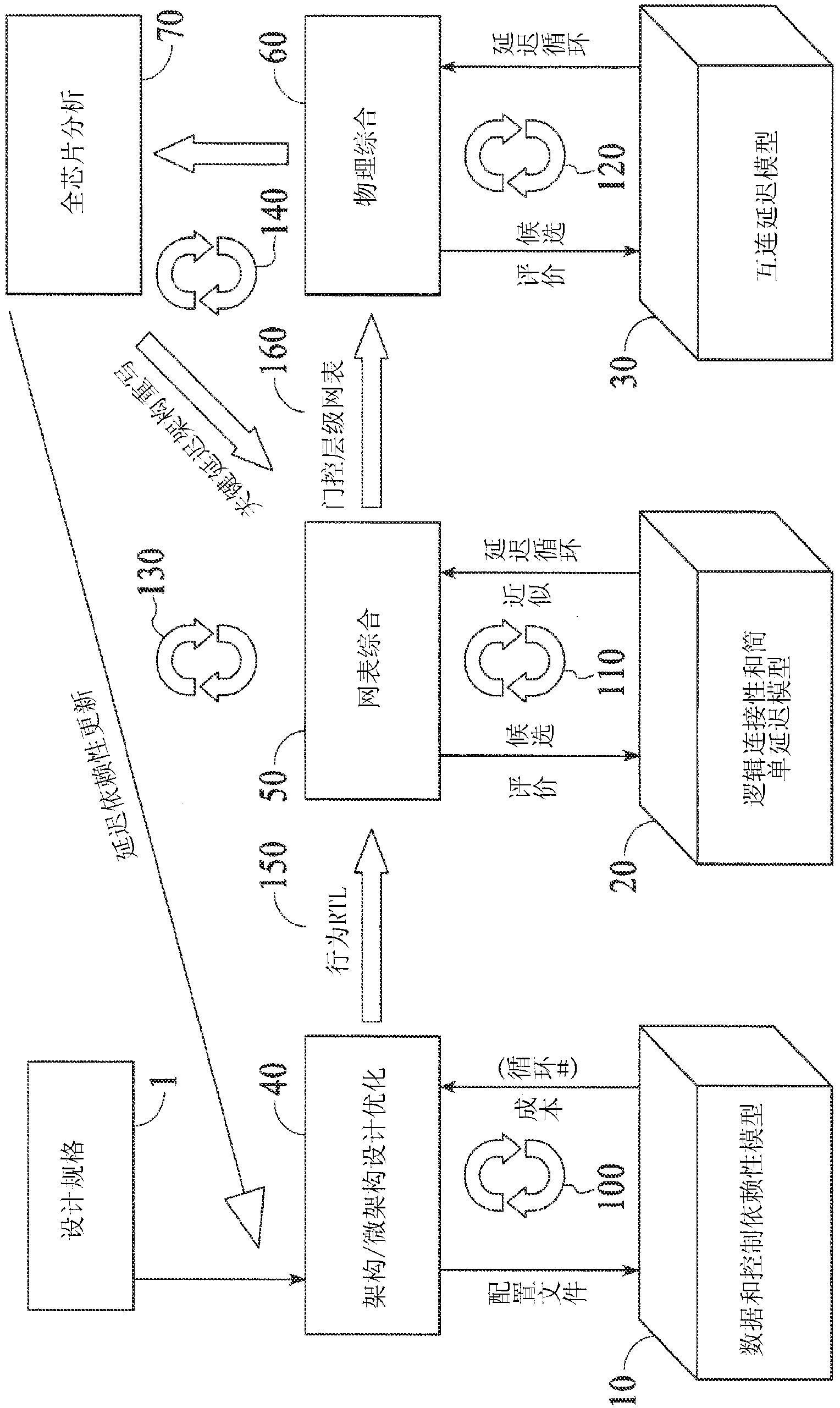

Integrated data model based framework for driving design convergence from architecture optimization to physical design closure

A data model, physical technology, applied in the framework field based on integrated data model used to drive design convergence from architectural optimization to physical design closure, can solve problems such as discontinuity of basic data model, and achieve the effect of alleviating the problem

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

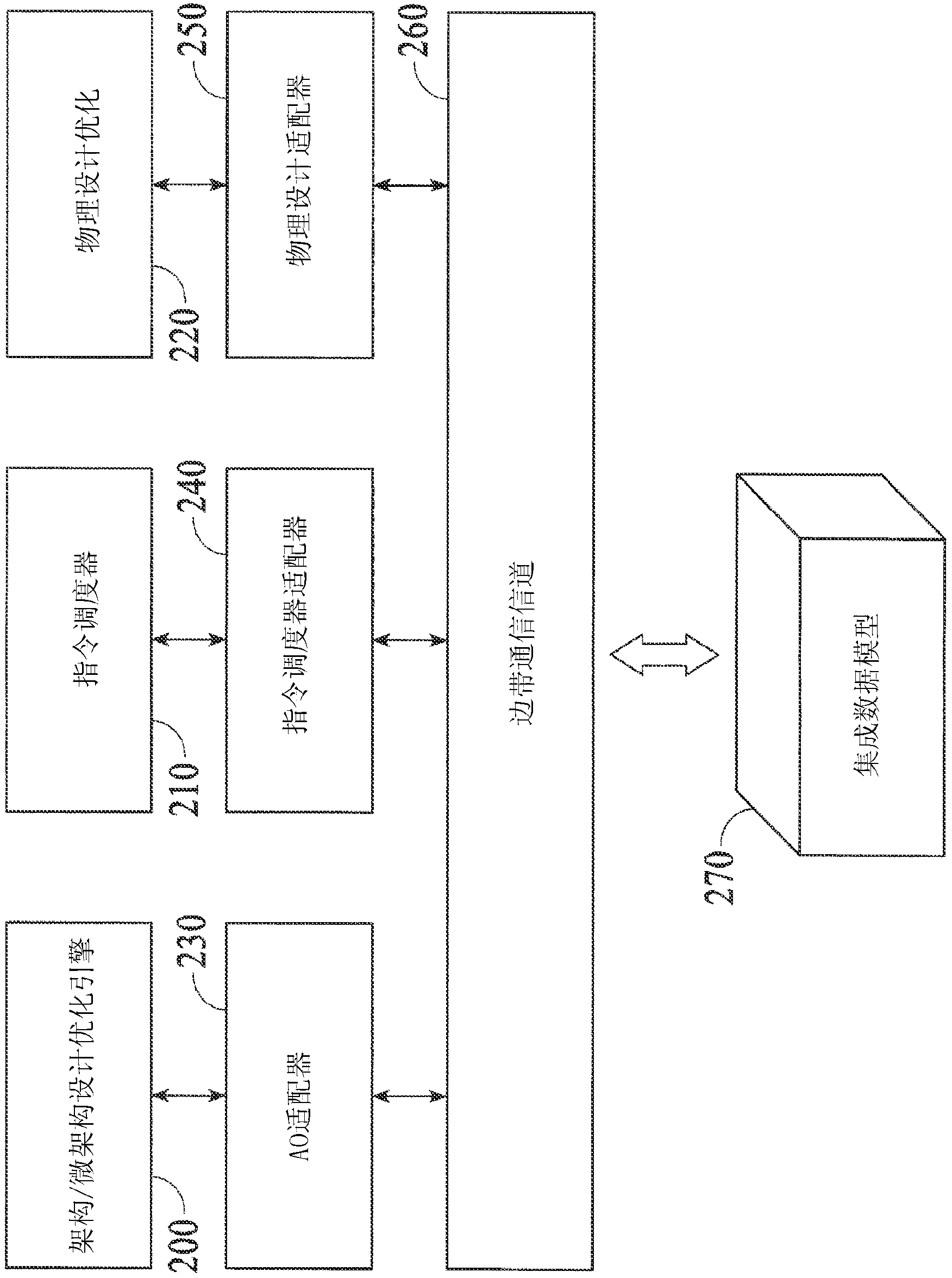

[0022] now turn to reference figure 2 , a framework with an Integrated Data Model (IDM) 270 is used according to one aspect of the invention. exist figure 2 , the architectural / microarchitectural design optimization engine 200 communicates with an architectural optimization (AO) adapter 230 . Additionally, instruction scheduler 210 may be in communication with instruction scheduler adapter 240 . Likewise, physical design optimization engine 220 communicates with physical design adapter 250 . Adapters 230 , 240 , and 250 communicate via sideband communication channel 260 , which communicates with integrated data model 270 .

[0023] The sideband communication channel 260 enables various optimization processes to communicate contextual information to a communication medium where such information is passively maintained continuously throughout the process. In the context of an EDA tool-based SoC design flow, this channel 260 is implemented using non-intrusive significant se...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More