Architectural level power-ware optimization and risk mitigation

A technology of power and processor architecture, applied in program control devices, software simulation/interpretation/simulation, CAD circuit design, etc., can solve problems such as long processing, costing millions of dollars, etc. Avoiding, high-performance effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

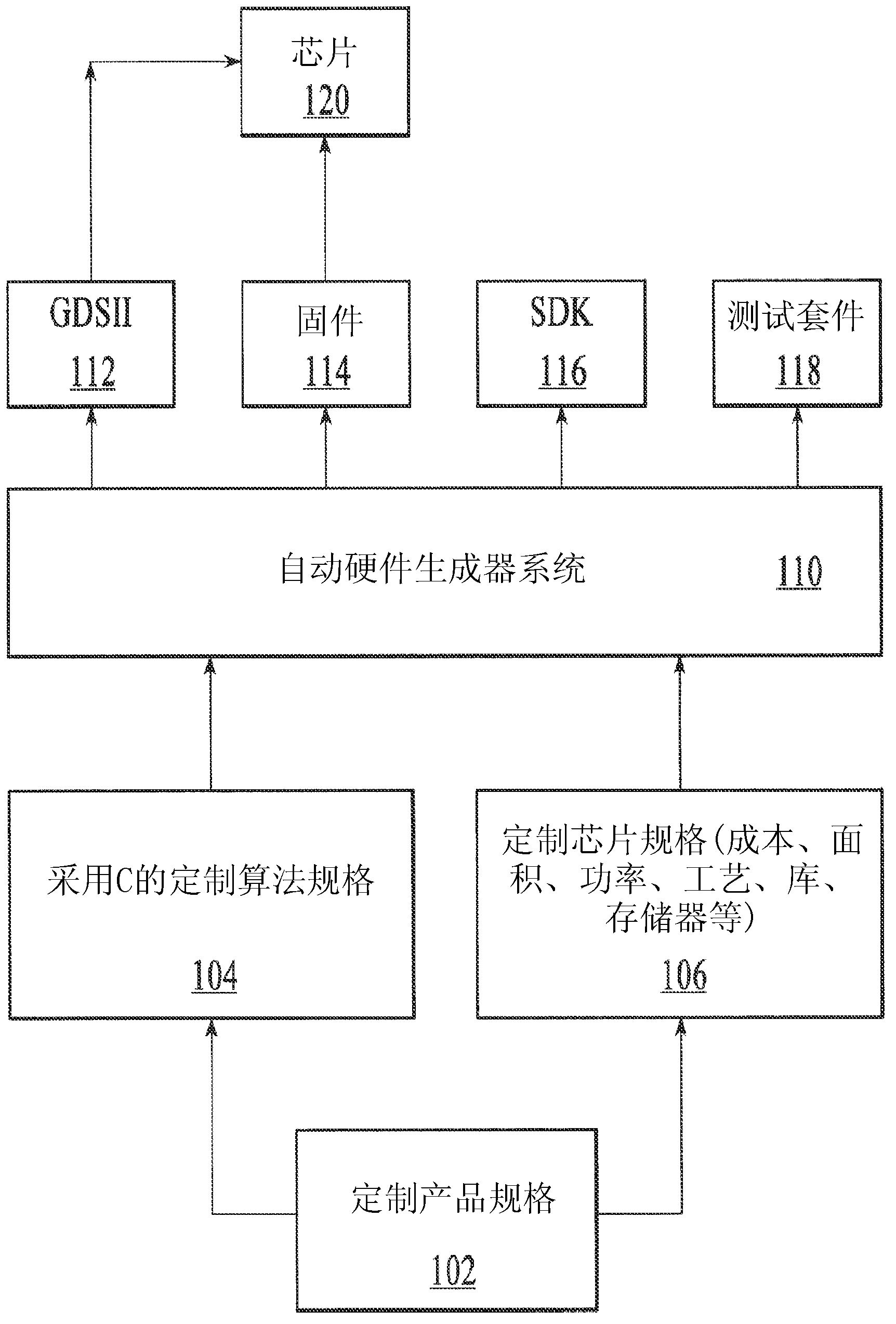

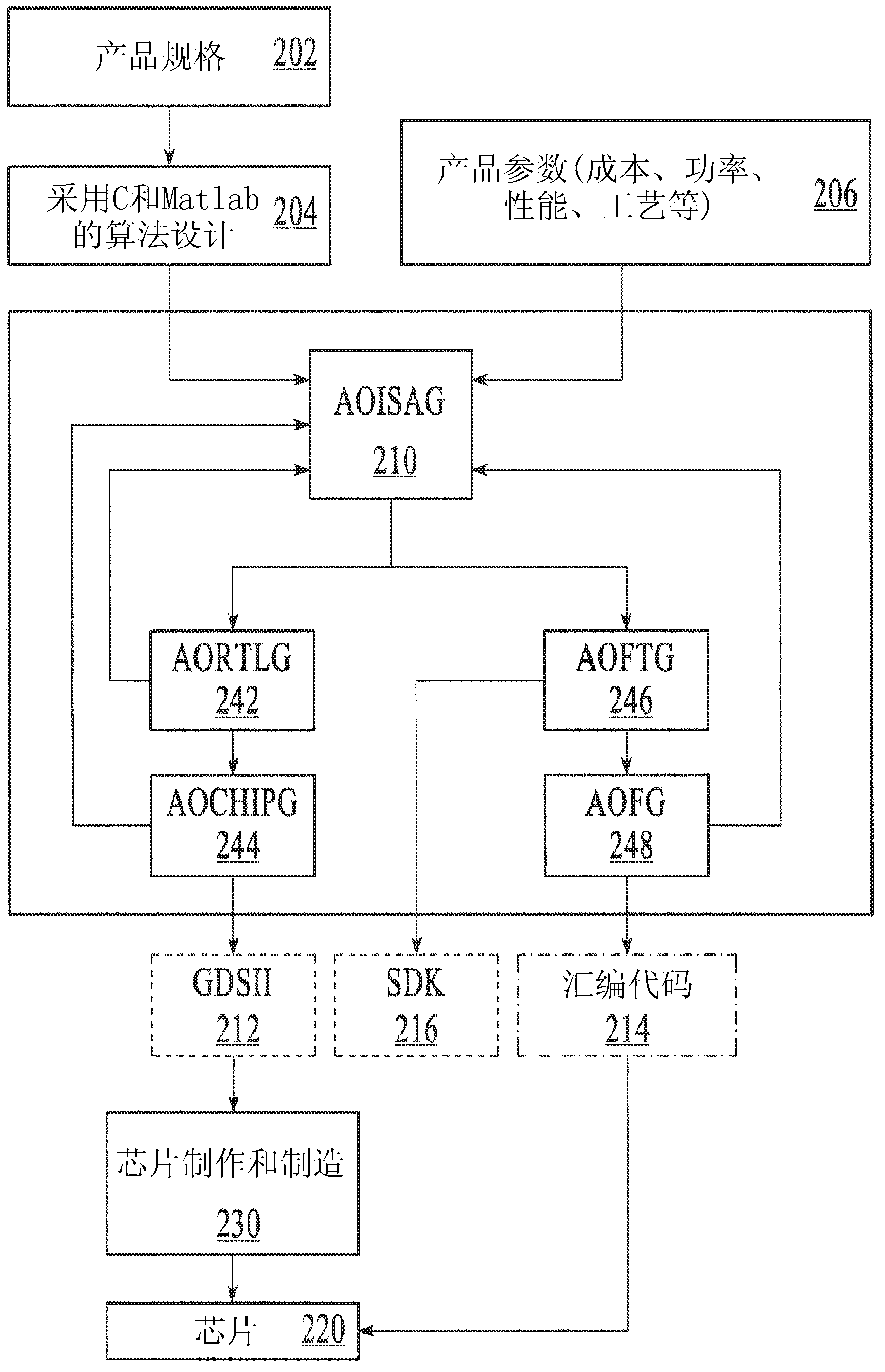

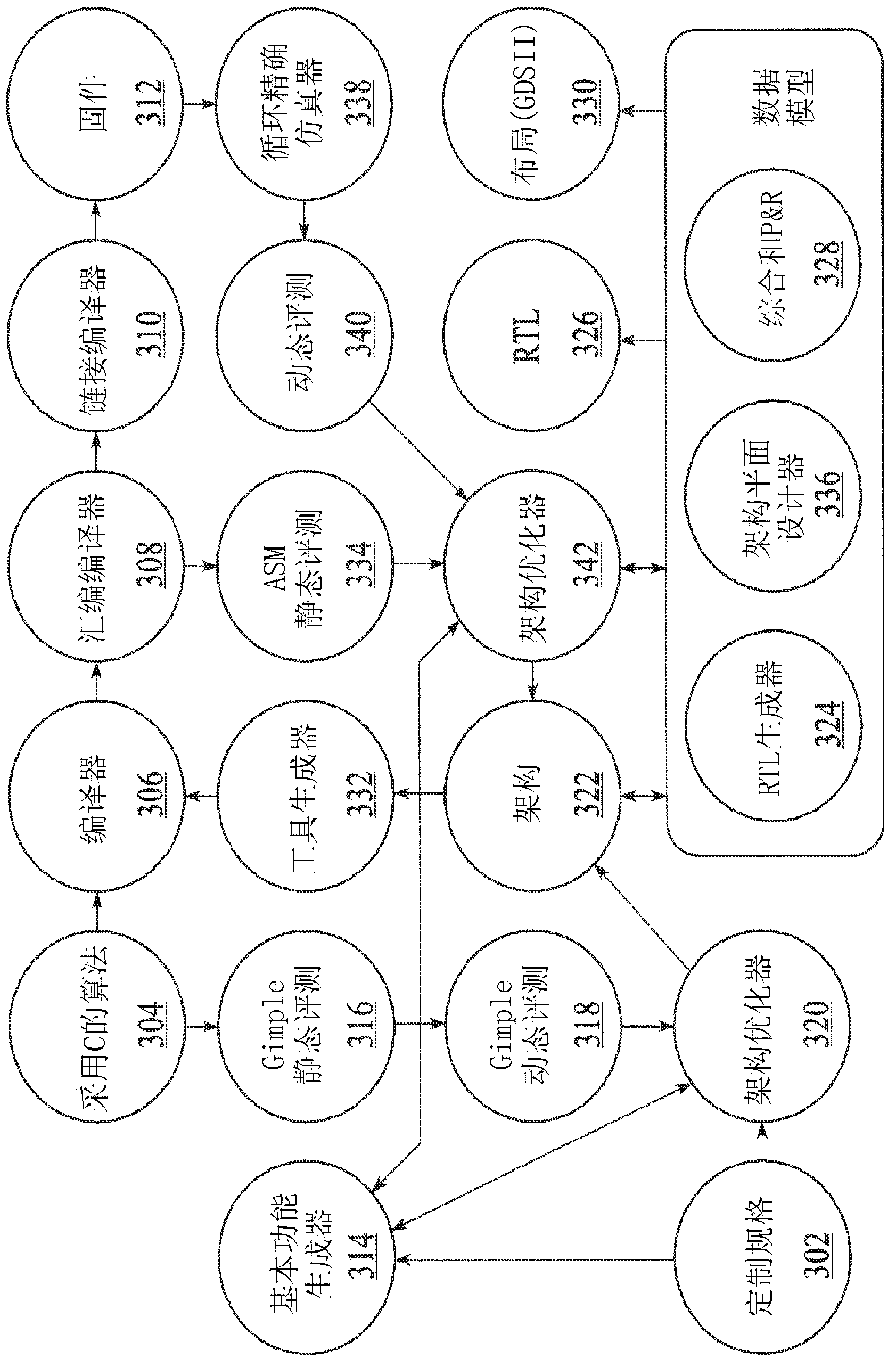

[0030] figure 1 An example system for automatically generating custom ICs is shown. figure 1 The system supports the automatic generation of the best customized integrated circuit solution for the selected target application. The specification of the target application program is usually realized by using a high-level language such as C, Matlab, SystemC, Fortran, Ada, or any other language to express an algorithm as a computer-readable code. The specification includes a description of the target application and also includes one or more constraints such as expected cost, area, power, speed, performance, and other attributes of the hardware solution. In order to assist the physical synthesis, the system encodes the "sideband" information into a netlist file, and can obtain design constraints (physical and timing) that are more effective in guiding the physical synthesis than the original user constraints alone. In certain embodiments, these constraints are "implied" through the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More