Chip thermal analysis method based on three-dimensional domain decomposition

A three-dimensional area, thermal analysis technology, applied in special data processing applications, instruments, electrical and digital data processing, etc. Speed, shortening time, temperature accurate effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

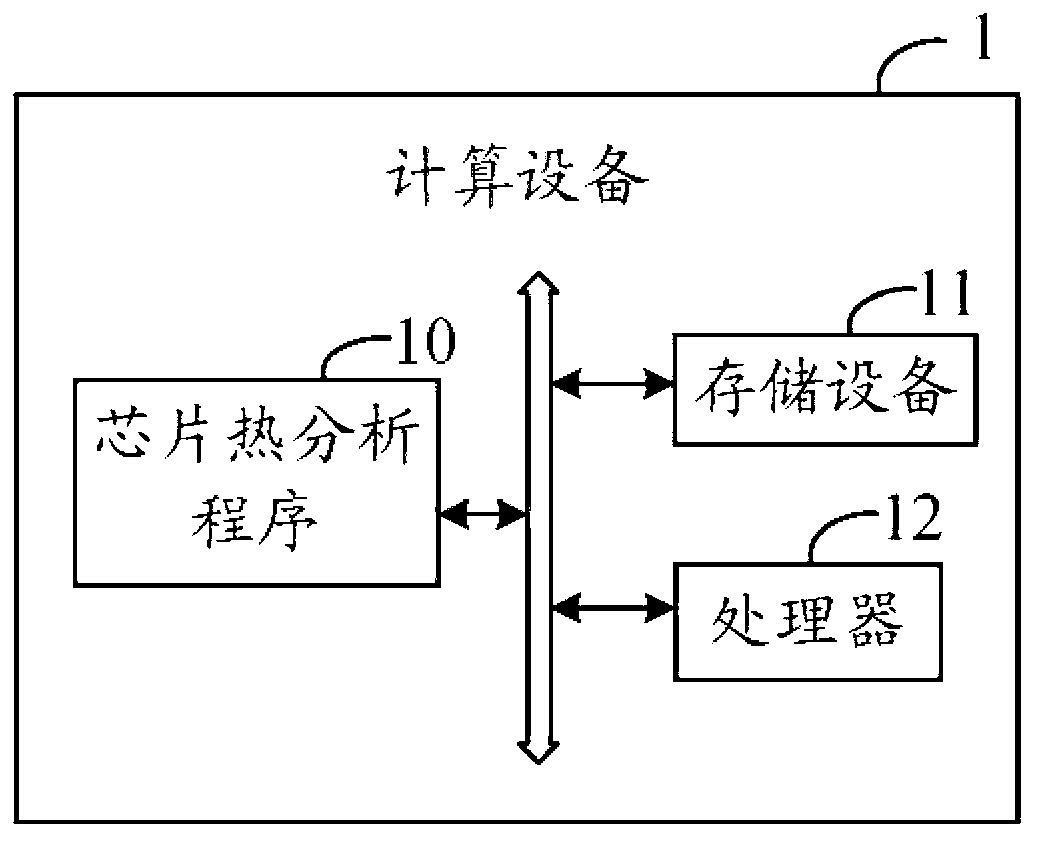

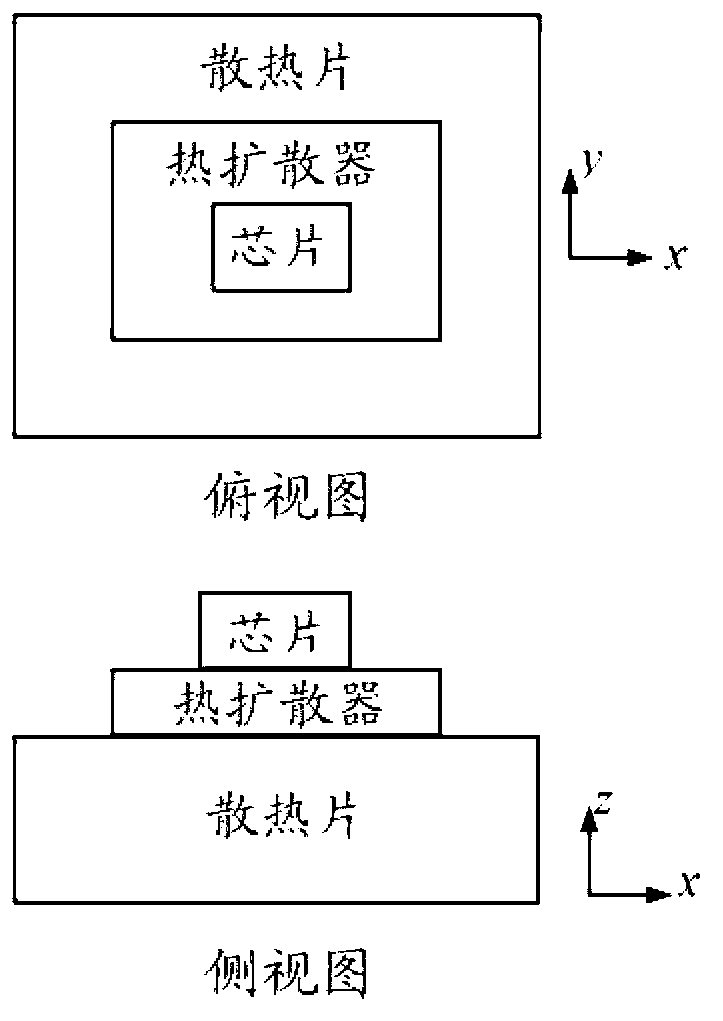

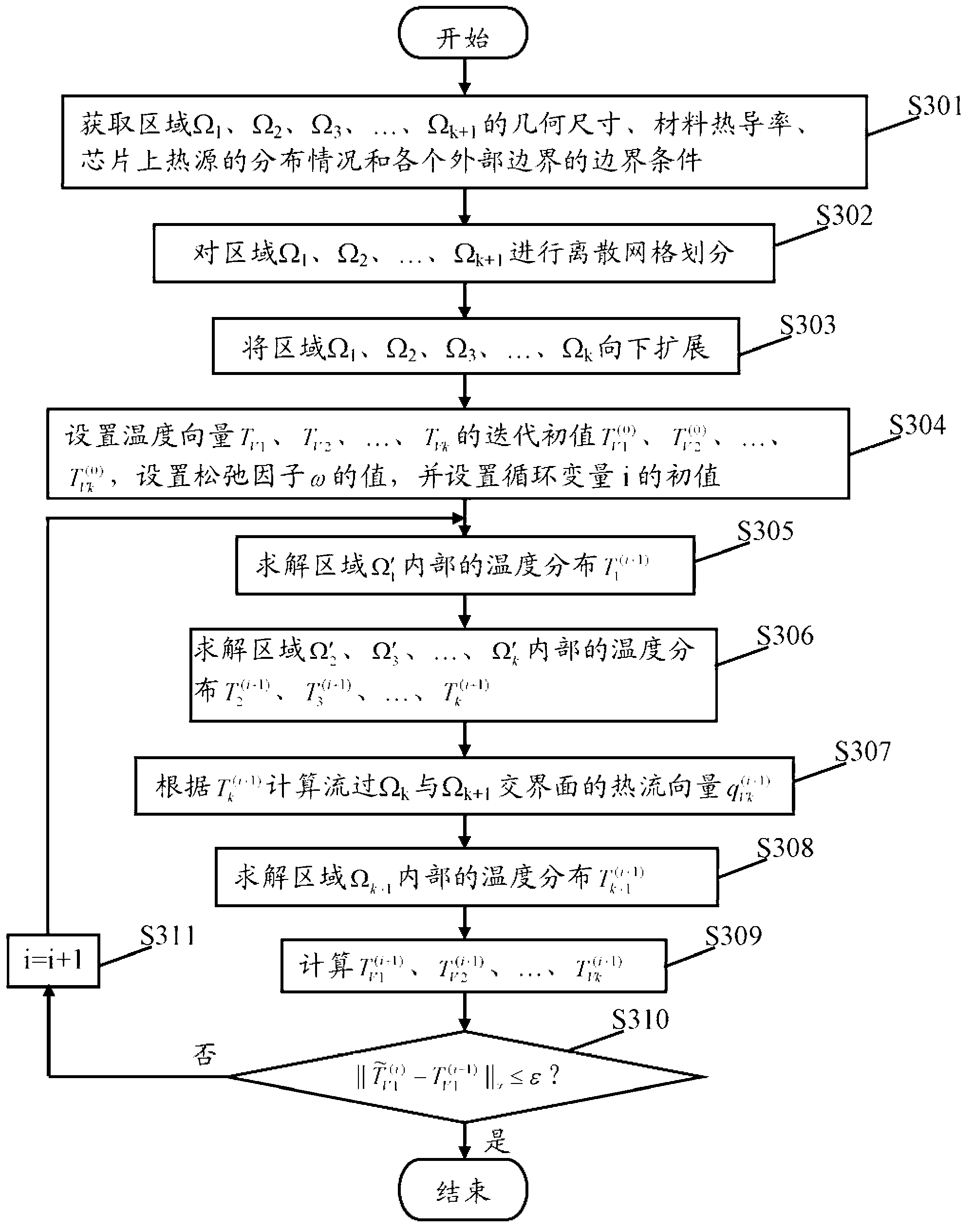

[0017] refer to figure 1 As shown, it is a schematic diagram of the application environment of a preferred embodiment of the chip thermal analysis method based on three-dimensional area decomposition of the present invention. The chip thermal analysis method based on three-dimensional domain decomposition is applied to the computing device 1 . The computing device 1 includes a chip thermal analysis program 10 , a storage device 11 and a processor 12 . The storage device 11 stores program codes of the chip thermal analysis program 10 and data required during operation. The processor 12 executes the program code of the chip thermal analysis program 10 to implement the chip thermal analysis method based on three-dimensional area decomposition, and calculate the temperature distribution of the chip in the chip system. The chip system includes a chip and k heat dissipation components (k≥1). The heat dissipation components include, but are not limited to, heat spreaders and heat ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More