A method for preparing sgoi or goi by using c-doped sige modulation layer

A modulation layer and doping concentration technology, applied in the field of semiconductor material preparation, can solve problems such as lattice mismatch, affecting SGOI or GOI performance, defects, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0040] Such as Figure 1 to Figure 6 As shown, this embodiment provides a method for preparing SGOI or GOI using a C-doped SiGe modulation layer, at least including the steps:

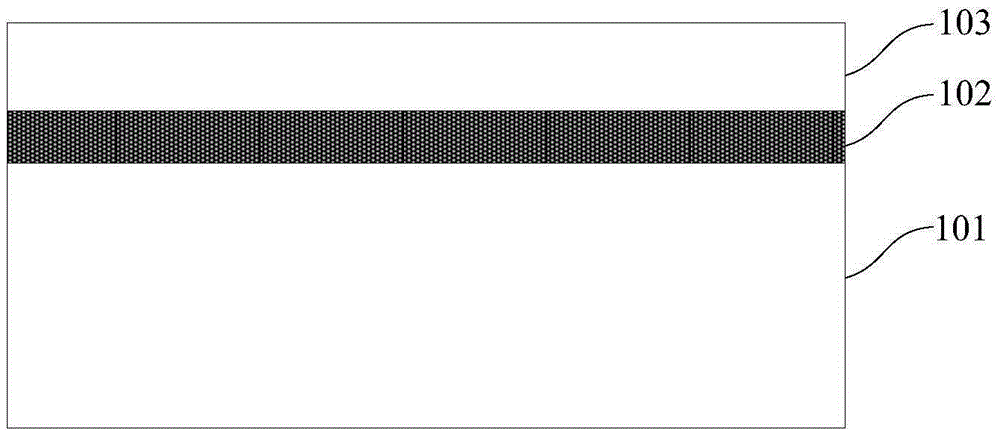

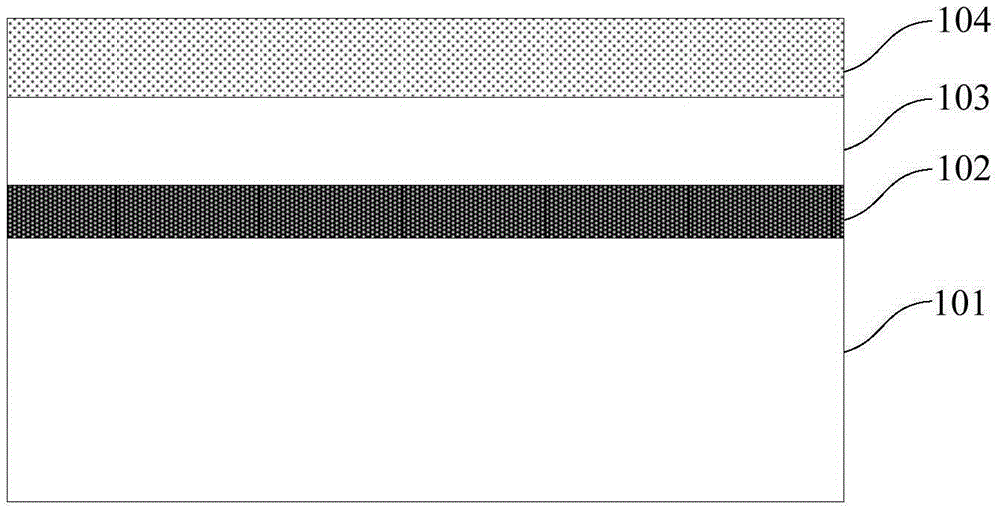

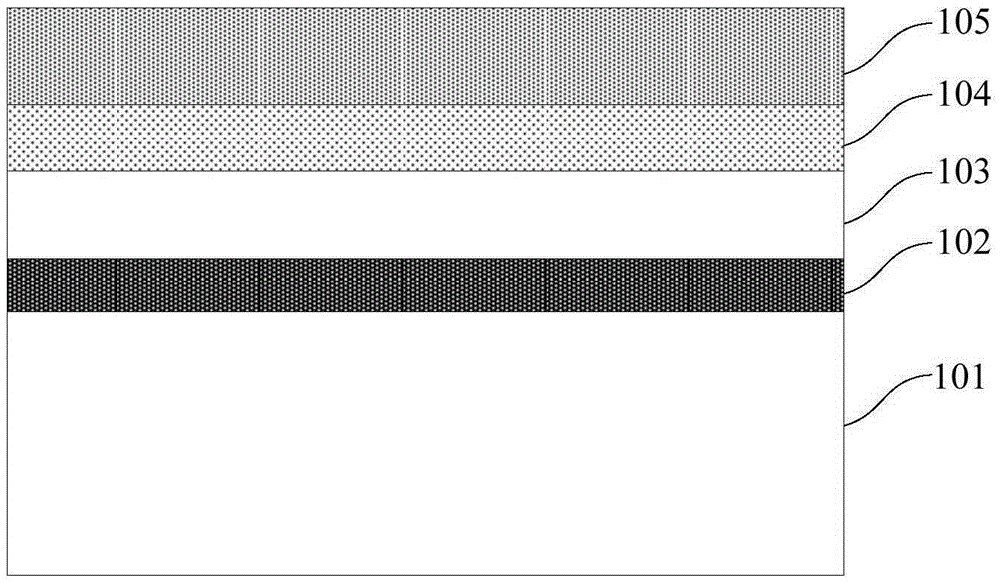

[0041] Such as Figure 1 ~ Figure 2 As shown, step 1) is performed first, providing an SOI substrate including a silicon substrate 101 , a buried oxide layer 102 and a top silicon layer 103 , and forming a C-doped SiGe modulation layer 104 on the surface of the top silicon layer 103 .

[0042] As an example, in the C-doped SiGe modulation layer 104, the doping concentration of C is not less than 1E20 / cm 3 . In this embodiment, in the C-doped SiGe modulation layer 104 , the doping concentration of C is constant. Specifically, in the C-doped SiGe modulation layer 104, the doping concentration of C is 3E20 / cm 3 .

[0043] As an example, the thickness of the C-doped SiGe modulation layer 104 is not less than 20 nm and not greater than its critical thickness. In this embodiment, the C-doped SiGe modula...

Embodiment 2

[0056] Such as Figure 1 to Figure 6 As shown, this embodiment provides a method for preparing SGOI or GOI using a C-doped SiGe modulation layer, the basic steps of which are as in Embodiment 1, wherein, in the C-doped SiGe modulation layer 104, the doping concentration of C is not However, it gradually decreases from bottom to top, that is, the C concentration near the top silicon layer 103 is high, and the C concentration near the SiGe material layer 105 is low, so that the top silicon layer 103 of SOI and the epitaxial SiGe material can be better adjusted. The lattice mismatch between the layers 105 reduces the generation of defects.

[0057] As mentioned above, the present invention provides a method for preparing SGOI or GOI by using a C-doped SiGe modulation layer, including the steps: 1) providing an SOI substrate including a silicon substrate, a buried oxide layer and a top silicon layer, and on the top Forming a C-doped SiGe modulation layer on the surface of the sil...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com