A phase detection and frequency multiplication logic circuit with error prevention mechanism

A logic circuit and phase detection technology, which is applied in the field of phase detection and frequency multiplication logic circuits, can solve problems such as incorrect output, delay, and precise signal noise, and achieve the effect of solving noise and delay, and preventing latch signal errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

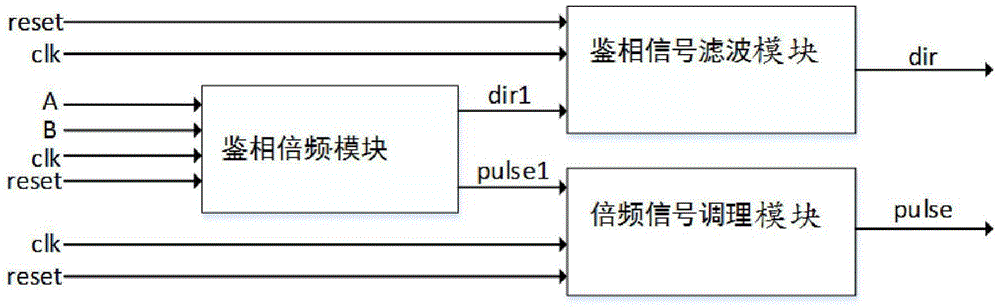

[0018] Such as figure 1 As shown, an embodiment of the present invention includes a phase detection and frequency multiplication module, and the phase detection and frequency multiplication module is connected with a phase detection signal filtering module and a frequency multiplication signal conditioning module.

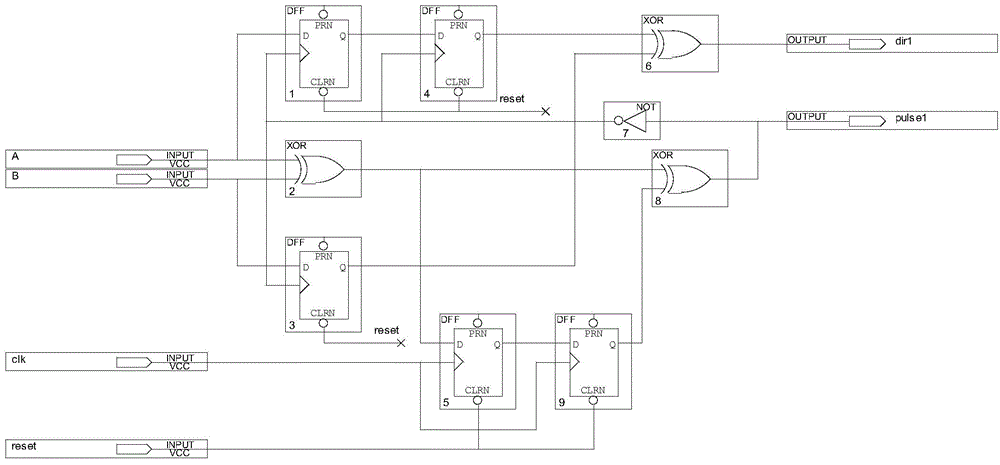

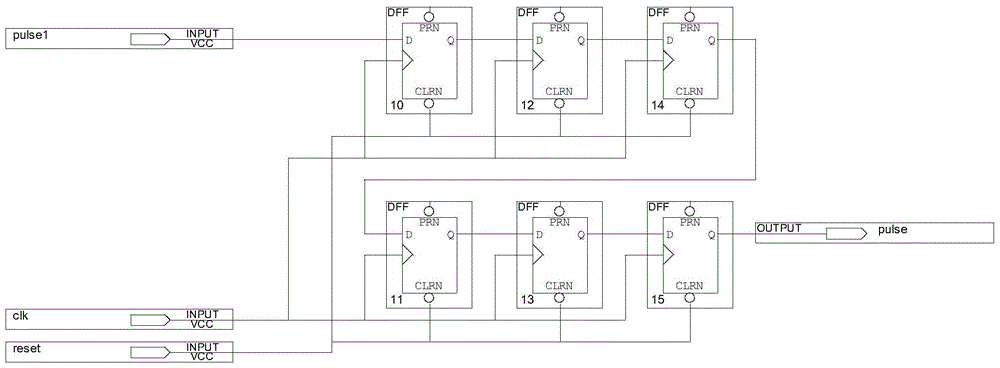

[0019] The phase detection and multiplication module uses five D flip-flops, three XOR gates, and one NOT gate. The phase detection part uses three D flip-flops, one XOR gate and one NOT gate, and the frequency multiplication part uses two D flip-flops and two XOR gates. The working principle of the phase detection part is that the signal is sent to the XOR gate operation after being delayed by the D flip-flop to obtain the initial phase detection signal, and the clock signal of the D flip-flop is the reversed signal of the initial frequency multiplication signal. The working principle of the frequency multiplication part is that after the signal is processed by t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More