Method for manufacturing circuit board layer-adding structure

一种增层结构、制造方法的技术,应用在微电子领域,能够解决精细线路成本高等问题,达到降低材料成本、降低基板成本、提高化学活性的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0094] The present invention will be further described in conjunction with accompanying drawing:

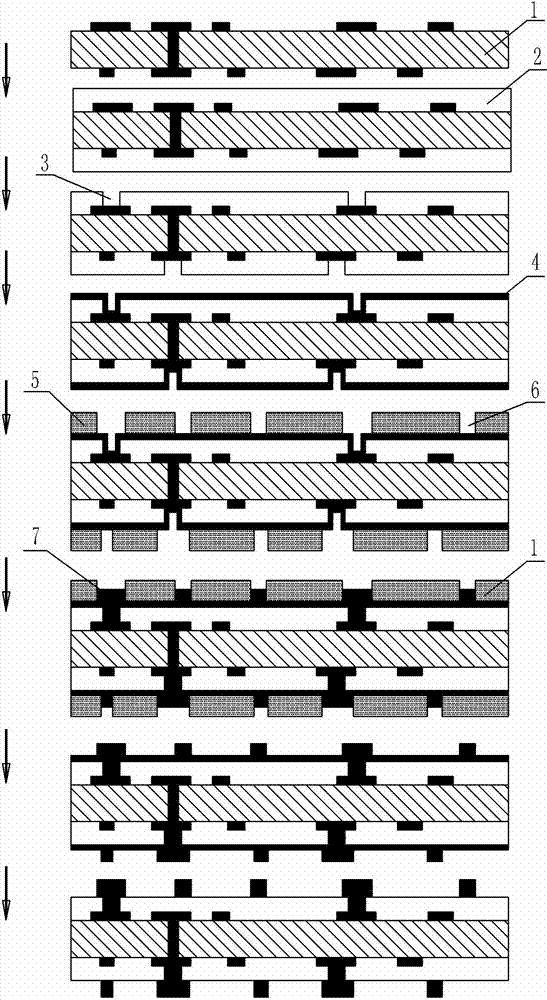

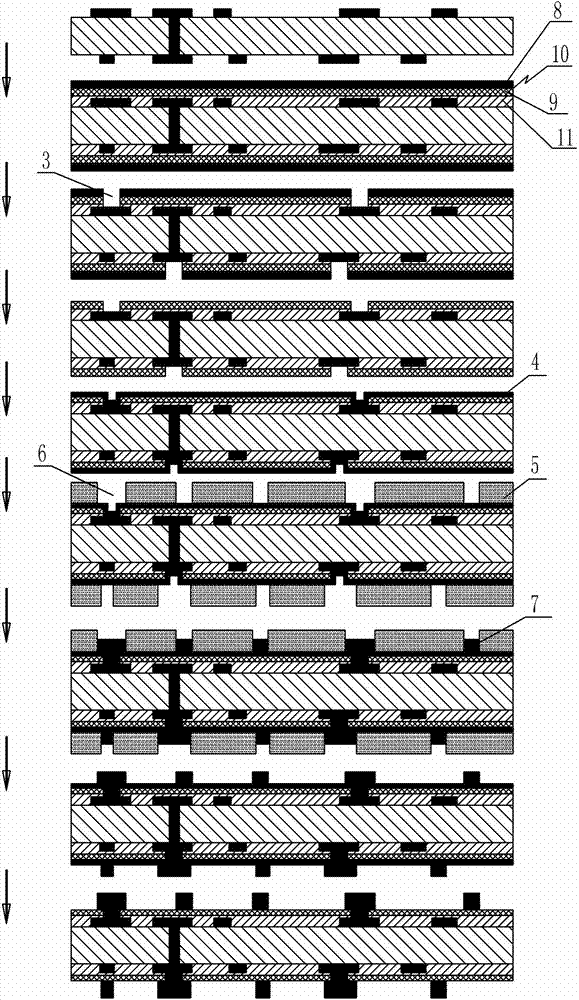

[0095] Figure 6 It is the semi-addition process flow of the present invention;

[0096] A method for manufacturing a circuit board build-up structure, comprising the following steps:

[0097] (1), see Figure 7 , production of inner layer circuit: make inner layer circuit 1, make metallized via hole 3 on the core board 2, make copper circuit 4 on both sides of the core board 2, the inner layer circuit of the package carrier board is wider, usually use the subtractive method to Finish;

[0098] (2), see Figure 8 , press the copper foil 4 and the prepreg 5 on both sides of the inner circuit 1 and solidify: press the copper foil 5 and the prepreg 6 on both sides of the inner circuit 1, and transfer the low-roughness structure on the surface of the copper foil 5 to the prepreg 6 ;

[0099] (3), see Figure 9 , Copper reduction: Thin the copper foil 5 to a thickness of 3um. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More