Gate driving circuit

A technology of gate drive circuit and level gate, which is applied in the direction of instruments and static indicators, can solve the problems of poor turn-off characteristics of switching elements, affecting the normal operation of the gate drive circuit, and disordered function of the gate drive circuit. The effect of reducing the risk of abnormality and reducing the threshold voltage offset

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

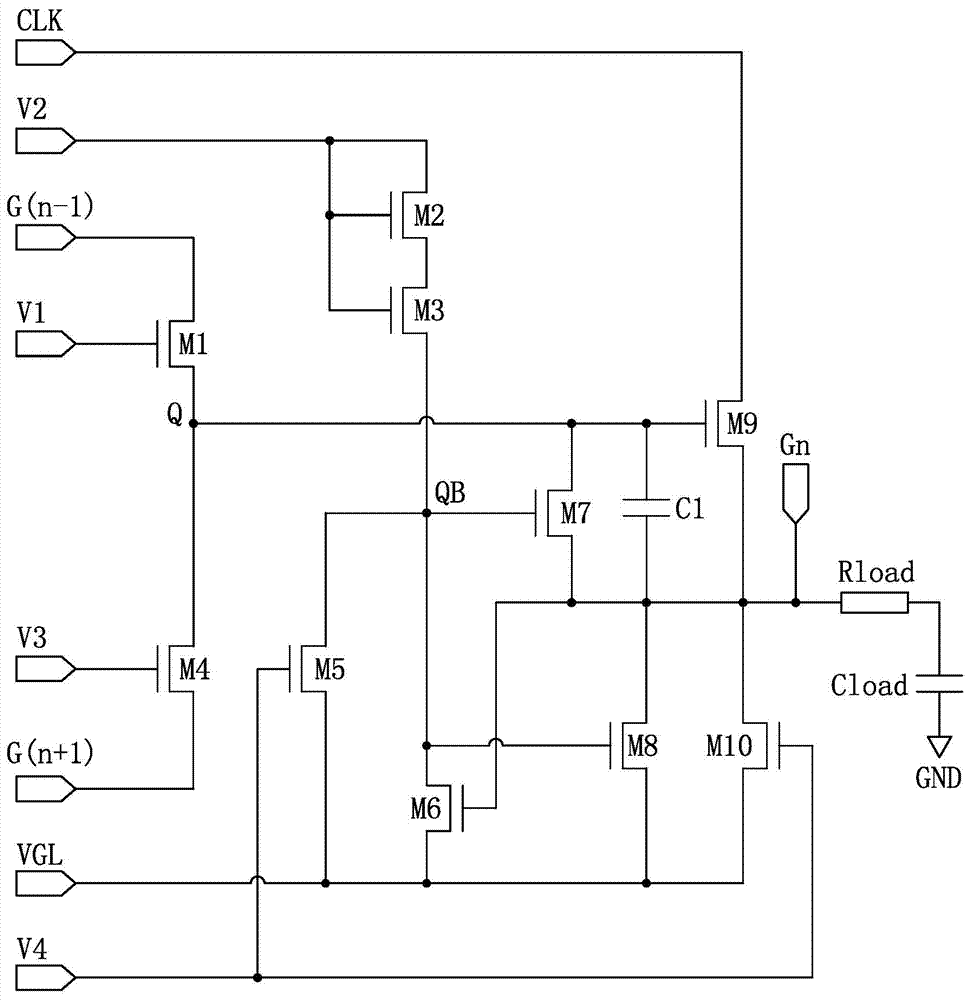

Method used

Image

Examples

no. 1 example

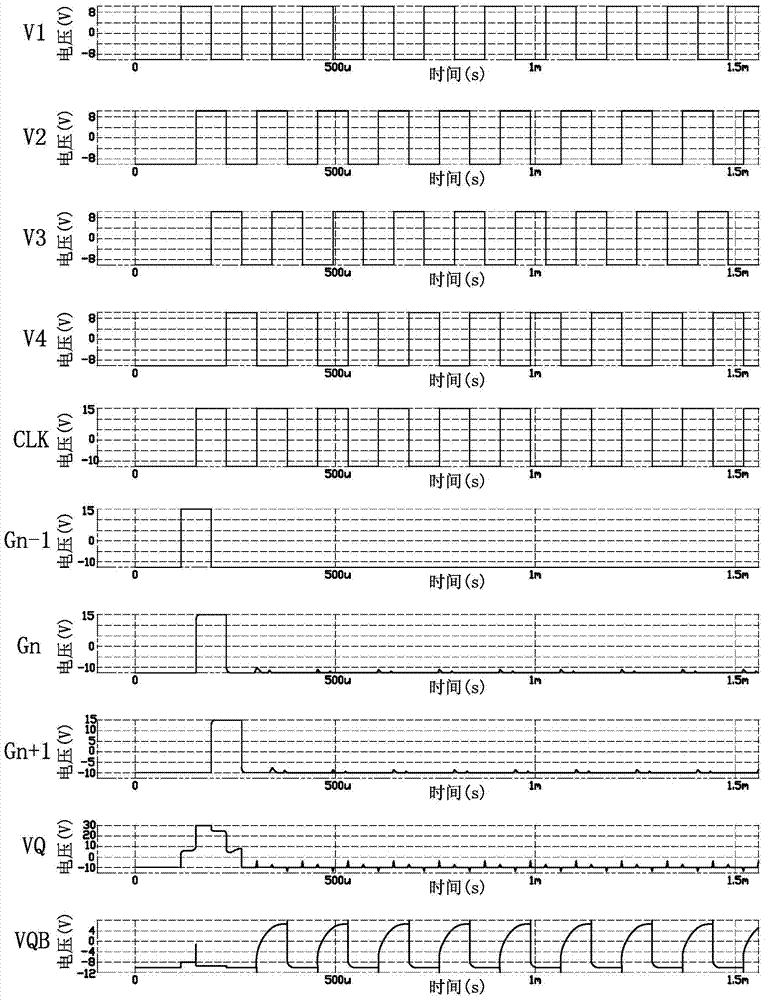

[0037] See figure 2 , Which is a timing diagram of the gate driving unit of the first embodiment, such as figure 2 As shown, the absolute values of the high level and low level of the first to fourth timing signals V1 to V4 are equal, and the duty ratios of the first to fourth timing signals V1 to V4 are all percent fifty. The first timing signal to the fourth timing signal V1 to V4 are delayed by a quarter of a period in turn, that is to say, the second timing signal V2 is one quarter period later than the first timing signal V1, and the third timing signal V3 is The second timing signal V2 is one quarter period later, and the fourth timing signal V4 is one quarter period later than the third timing signal V3. The fifth timing signal CLK is synchronized with the second timing signal V2.

[0038] In an embodiment of the present invention, the high level of the first to fourth timing signals V1 to V4 is 10 volts (V), the high level of the fifth timing signal CLK is 15V, and t...

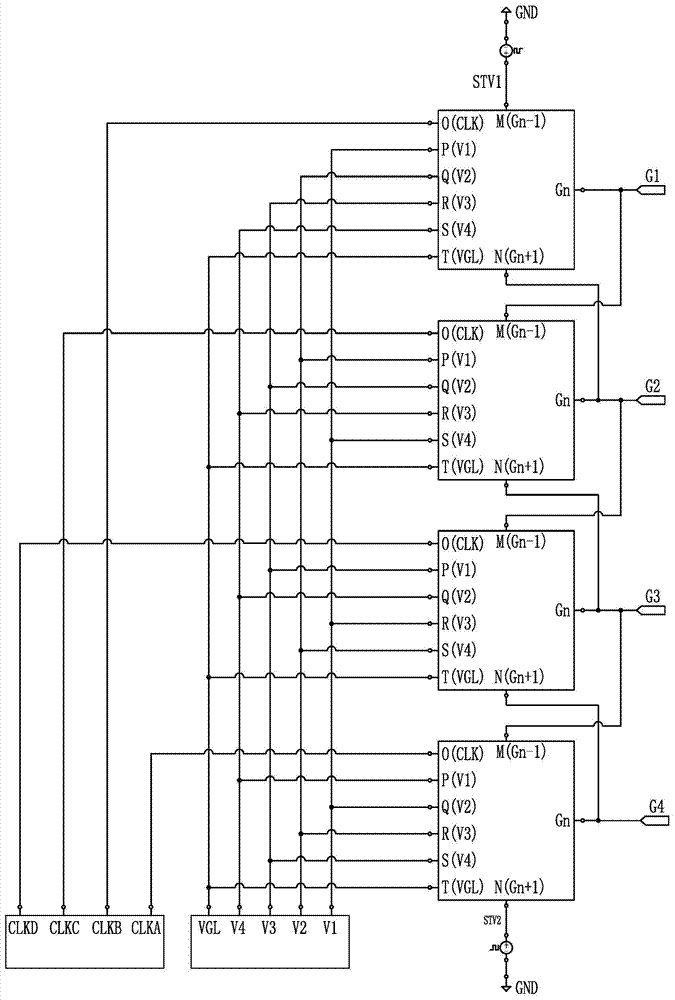

no. 2 example

[0058] Figure 5 It is a timing diagram of the four-stage gate driving unit in the gate driving circuit of the second embodiment of the present invention. Such as Figure 5 As shown, the high level of the first to fourth timing signals V1 to V4 is three times the absolute value of the low level, and the duty ratios of the first to fourth timing signals V1 to V4 are all 100 Twenty-five. That is, the product of the amplitude of the high level and the duration of the high level of the first to fourth timing signals V1 to V4 is equal to the product of the amplitude of the low level and the duration of the low level, so The first to fourth switching elements M1 to M4, the fiftieth switching element M5, and the tenth switching element M10 have a voltage offset when a positive voltage is applied and a threshold voltage offset when a negative voltage is applied. As a result, the left and right deviation of the threshold voltage in the gate drive unit can be offset, so that the thresho...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More