Method for increasing reading and writing speeds of NAND flash controller

A technology of read and write speed and controller, applied in instruments, memory systems, memory address/allocation/relocation, etc., can solve the problems of underutilization of chip cache resources, reduce read and write speed, increase cost, etc., and achieve flexible cache Operation mode, the effect of improving the reading and writing speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

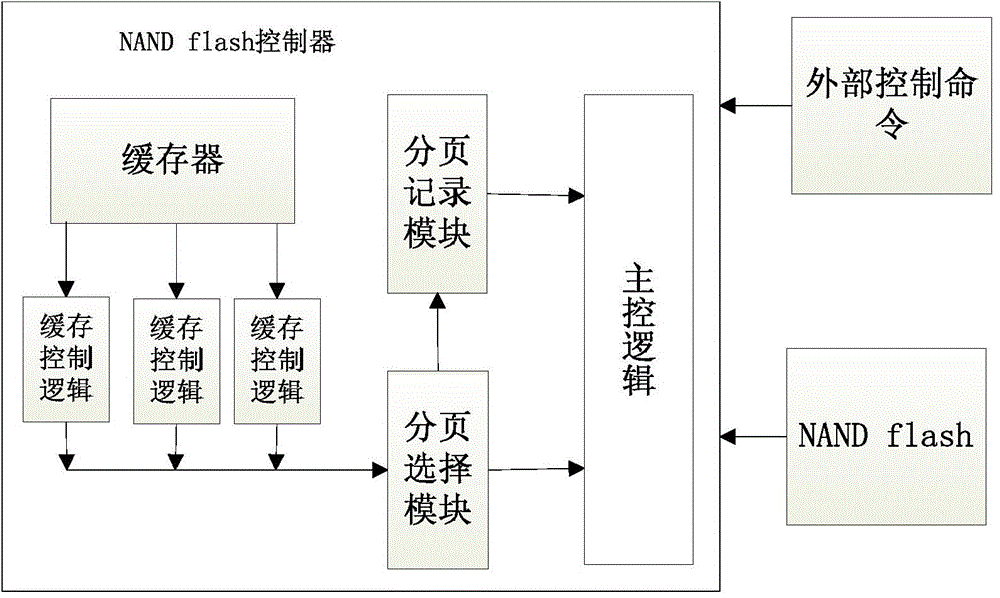

[0026] Such as figure 1 As shown, a method for improving the read and write speed of the NAND flash controller is realized by the following system, the system includes the NAND flash controller, NAND flash and external control commands, one end of the NAND flash controller is connected to the system bus, and the other end It is directly connected with NAND flash, and external control commands can directly operate the NAND flash controller; the NAND flash controller includes main control logic, a buffer, multiple sets of cache control logic, a paging selection module and a paging recording module, the main control logic With ECC verification module; the cache is used to cache the read and write data, and the cache control logic is connected with the cache for dynamic allocation of the cache; the paging selection module is connected with the cache control logic and the main control logic for Select the currently used cache page in the cache page, which can be set by an external ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More