Circuit structure capable of preventing internal memory cell of memory chip from being rewritten during powering up or down

A memory chip and internal storage technology, applied in static memory, digital memory information, information storage, etc., can solve the problems that the reset threshold voltage and reset time cannot be improved, and achieve the effect of low cost and simple circuit structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

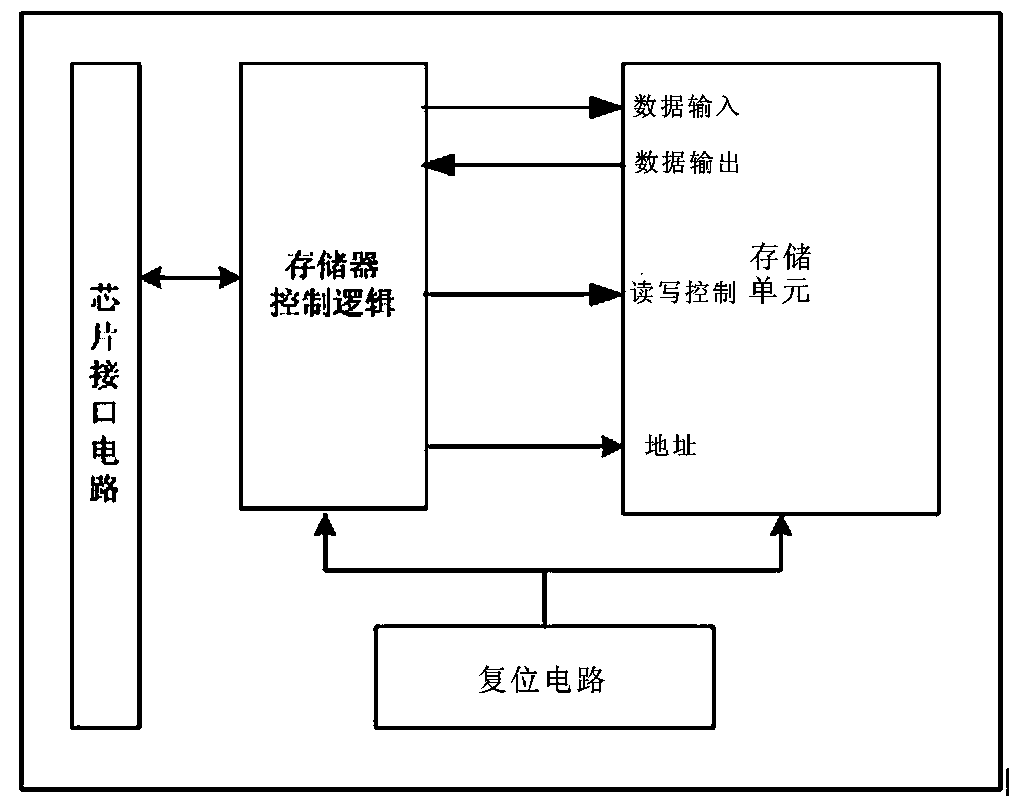

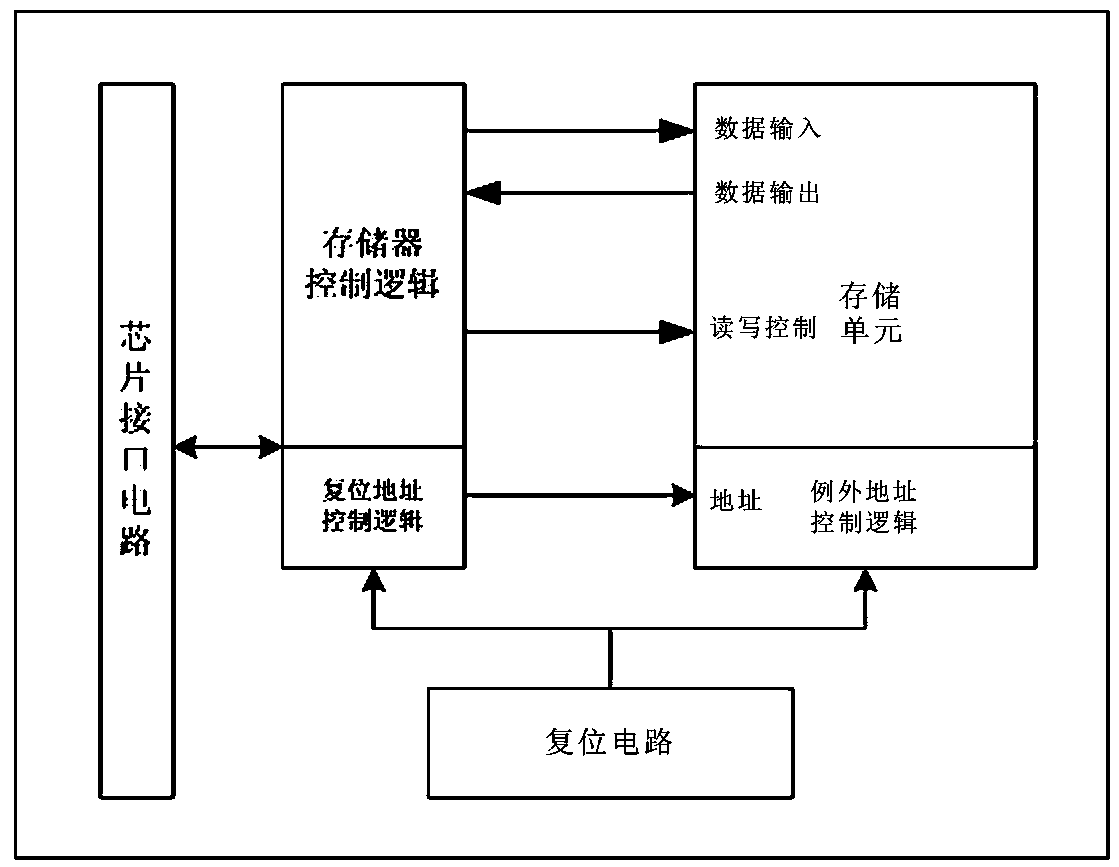

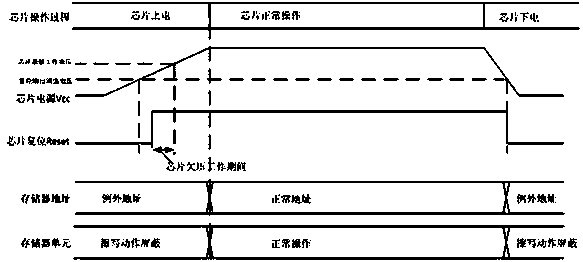

[0012] See figure 2 As shown, a circuit structure for preventing power-on and power-off of the internal storage unit of the memory chip from being rewritten, which includes a reset circuit, the reset circuit is connected to the memory control logic circuit and the storage unit, and the storage unit is connected to the memory control logic circuit through control lines, address lines, and data lines , the memory control logic circuit is connected to the chip interface circuit, a reset address control logic circuit is set on the memory control logic circuit; an exception address control logic circuit is set on the storage unit, the reset address control logic circuit is connected to the exception address control logic circuit, under the input of the exception address Therefore, even if the erasing and writing control signal of the storage unit exists, there will be no memory of the erasing and writing action, which better ensures that the storage unit of the memory chip will not...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap