Graph optimization method for short-circuit path in integrated circuit layout verification

A technology of integrated circuits and graphics, used in electrical digital data processing, special data processing applications, instruments, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

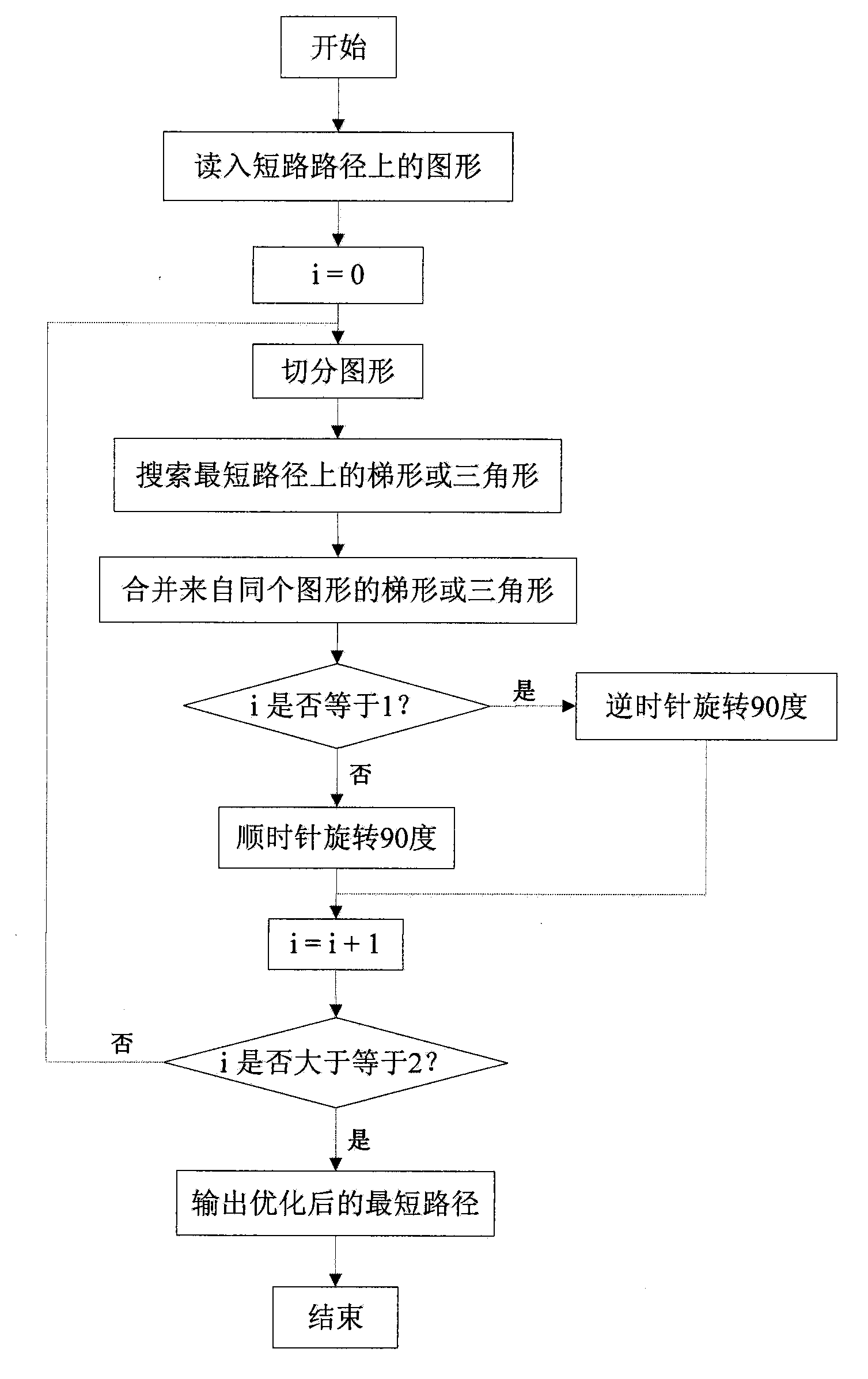

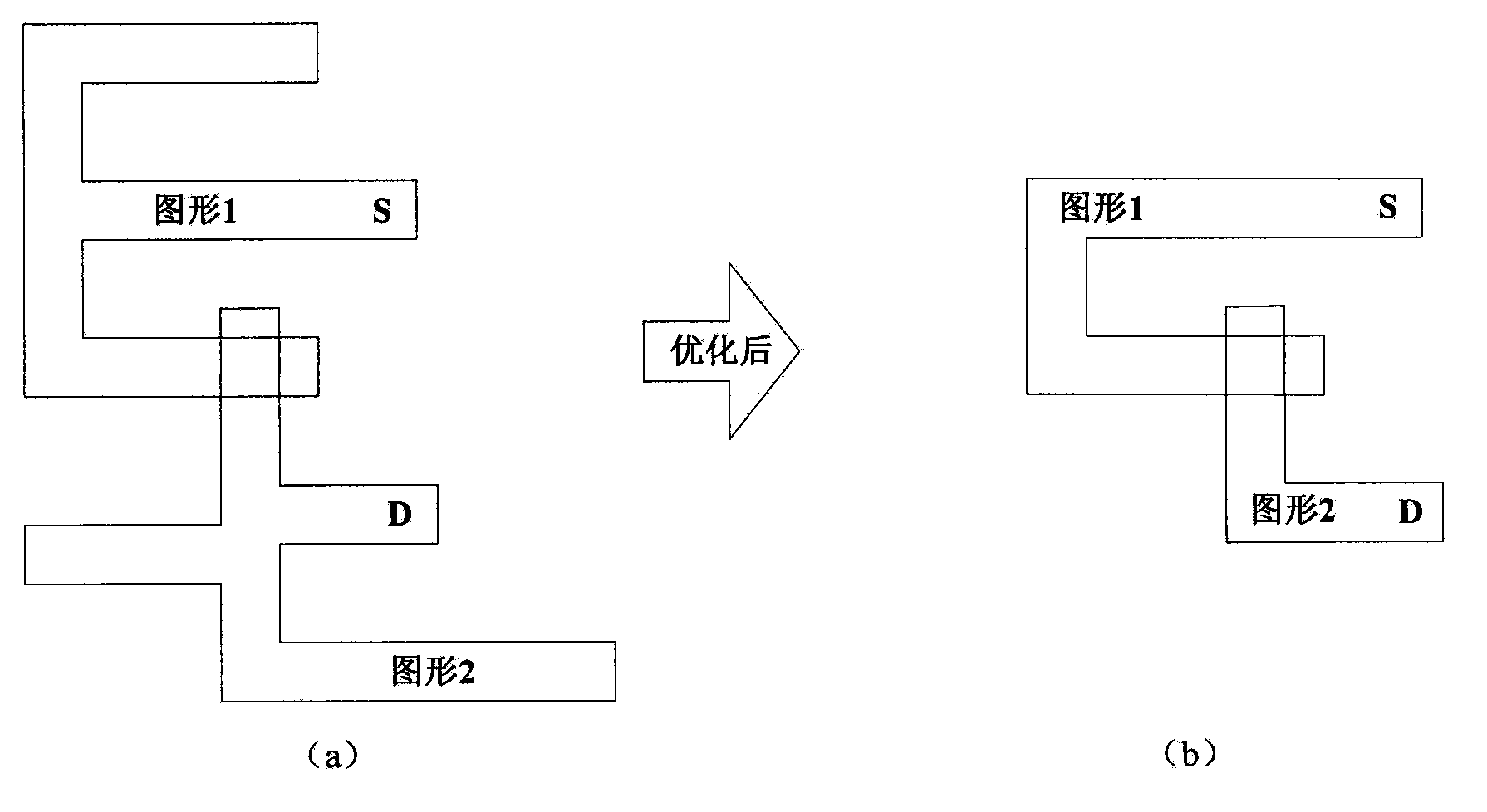

[0019] The processing flow of this method is as follows Figure 1 Show. Introduce the concrete implementation of this method below in conjunction with example, as figure 2( As shown in a), potential S and potential D are short-circuited by connecting graph 1 and graph 2, but graph 1 and graph 2 cannot visually represent the connection of the short-circuit path, especially when there are many and complex graphs on the short-circuit path , it is difficult to intuitively represent the connection relationship of the short-circuit path. The optimized results of this method are as follows figure 2( As shown in b), by optimizing the graphics on the short-circuit path, the representation of the short-circuit path is more intuitive and concise. The following combination Figure 2 The example shown introduces the specific steps of this method:

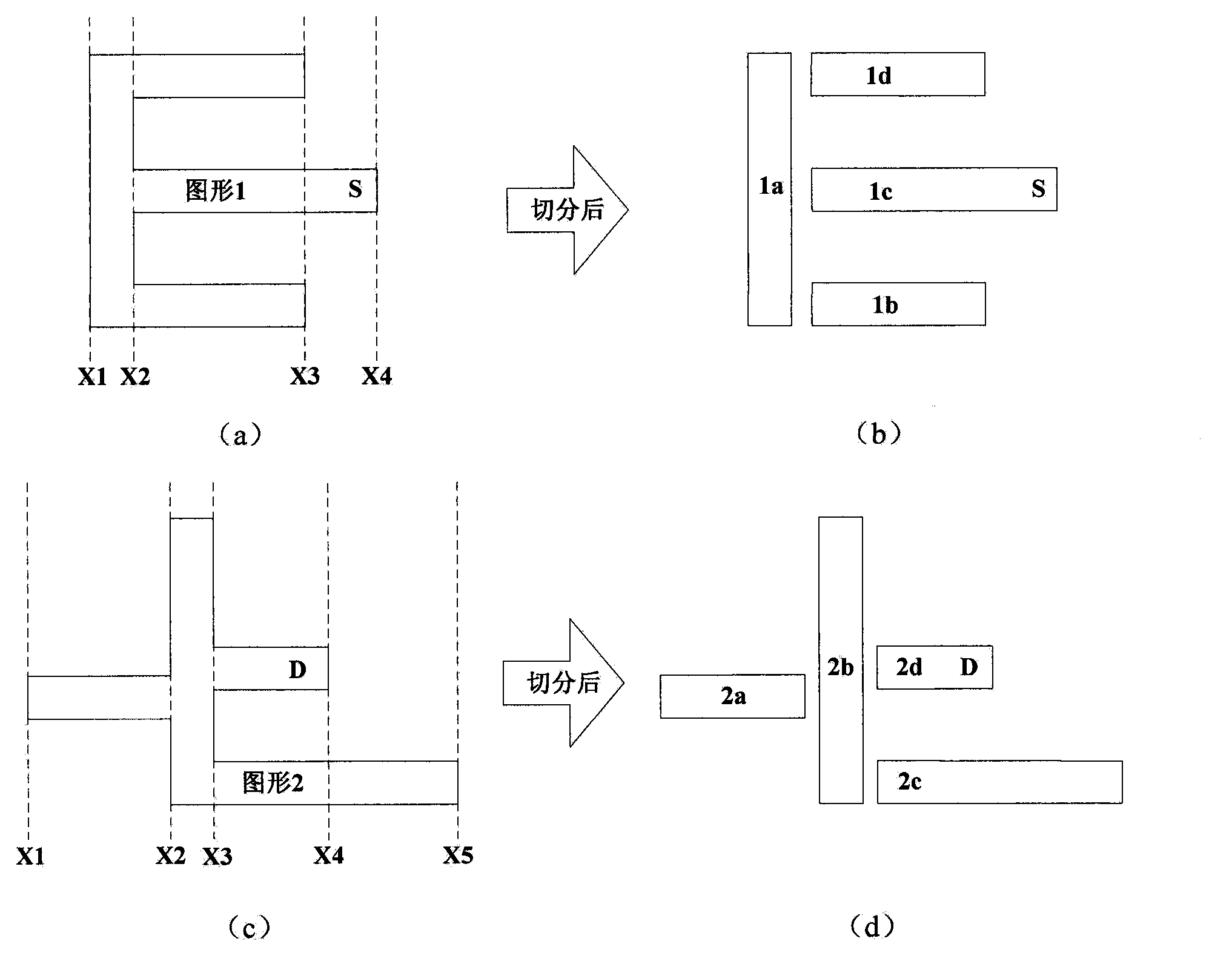

[0020] Step 1: Use the scanning line method to segment the graphics. The segmentation of graph 1 is as follows image 3( As shown in a)...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More