Low-dropout linear voltage stabilizer

A low-dropout linear and voltage regulator technology, applied in the direction of instruments, regulating electrical variables, control/regulation systems, etc., can solve problems such as deterioration, achieve the effect of improving PSRR and increasing circuit stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The implementation of the present invention is described below through specific examples and in conjunction with the accompanying drawings, and those skilled in the art can easily understand other advantages and effects of the present invention from the content disclosed in this specification. The present invention can also be implemented or applied through other different specific examples, and various modifications and changes can be made to the details in this specification based on different viewpoints and applications without departing from the spirit of the present invention.

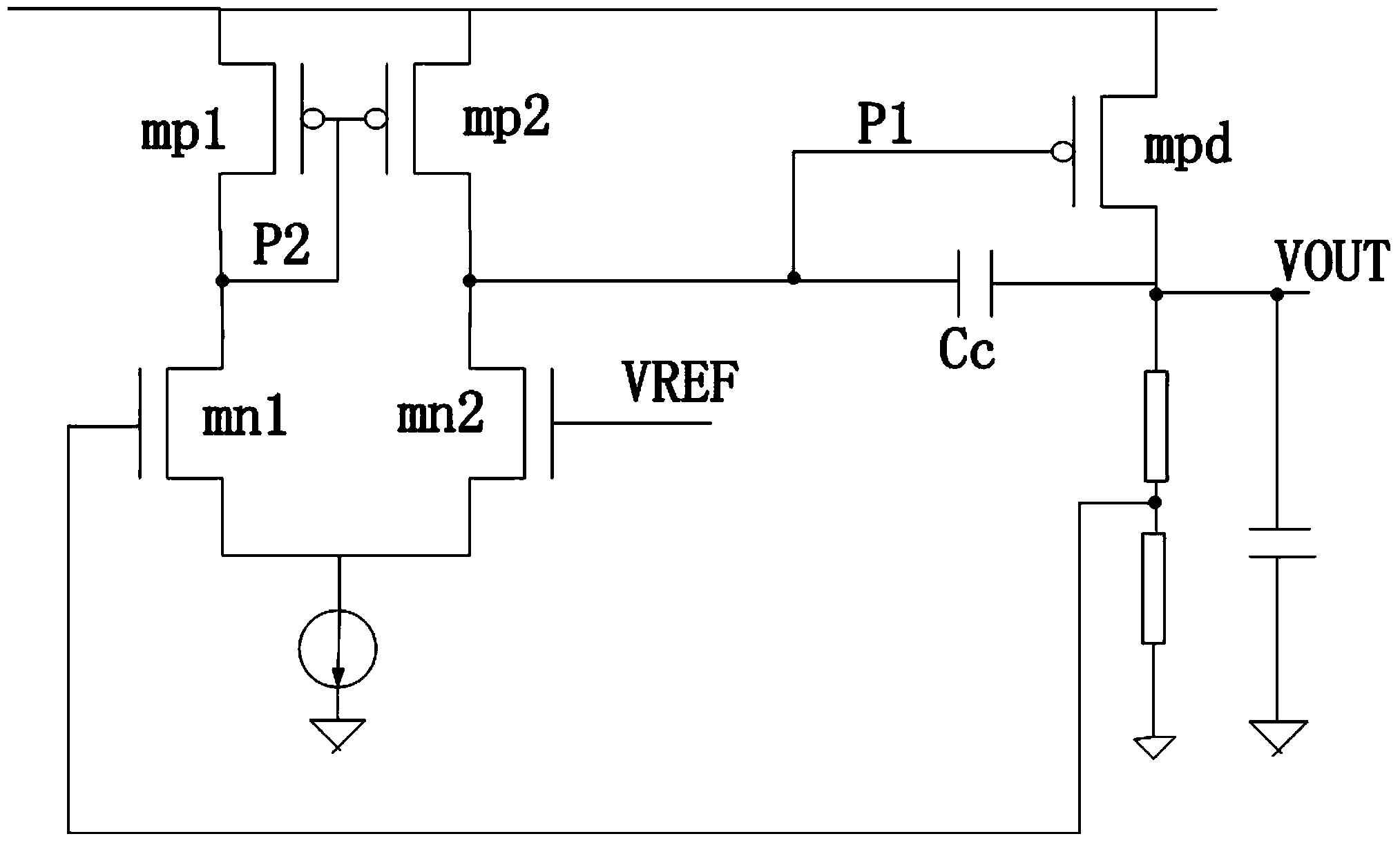

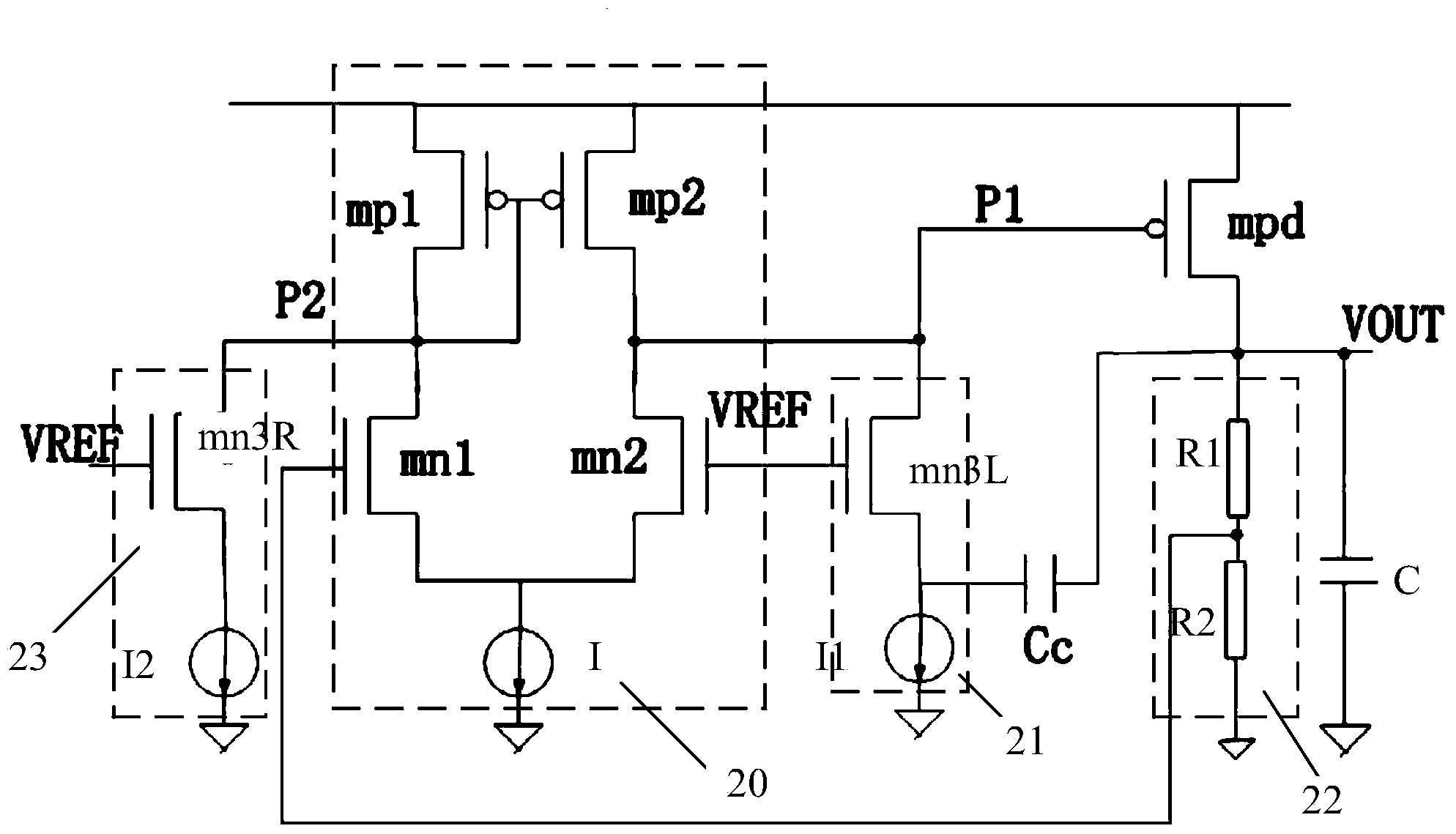

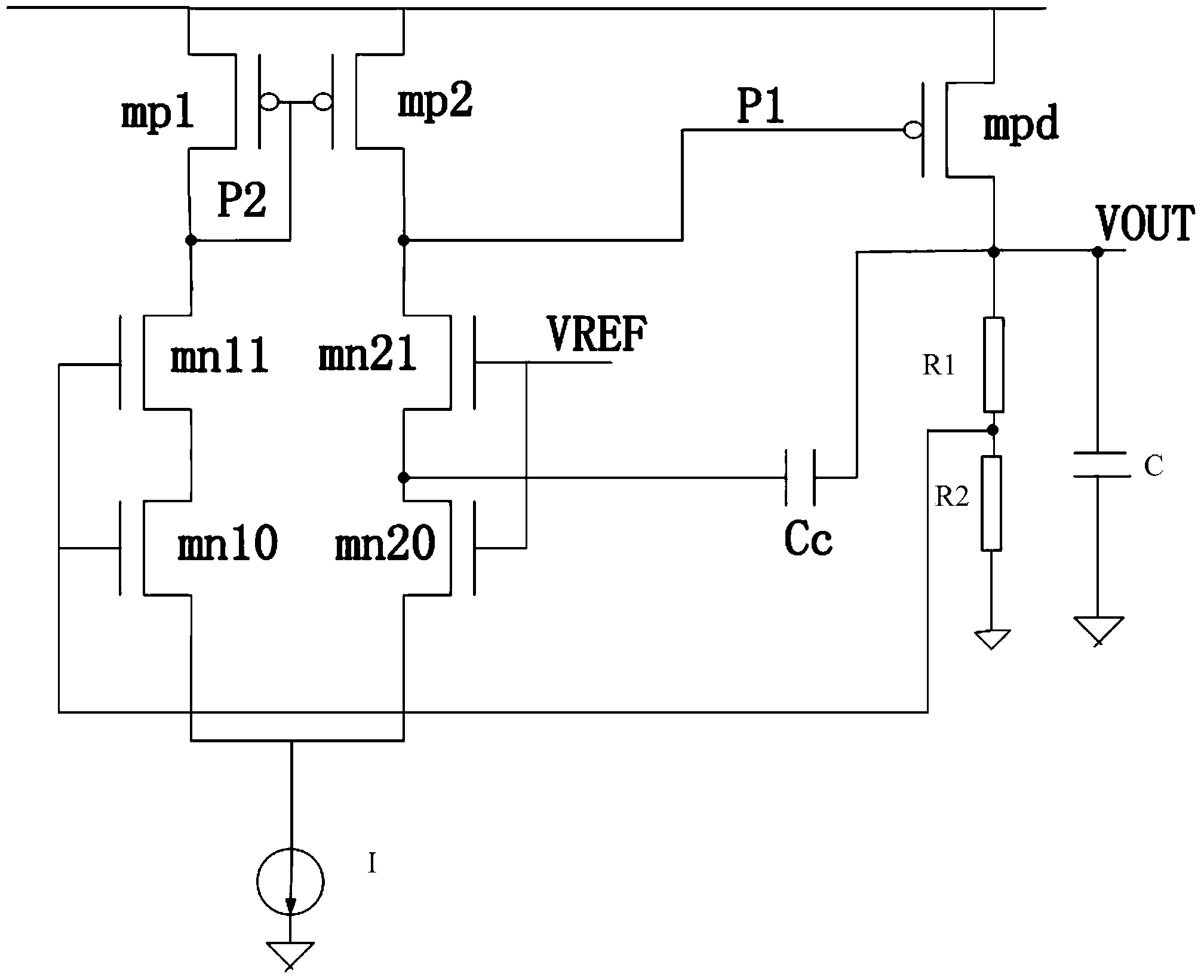

[0020] A low-dropout linear voltage regulator of the present invention adds a common-gate amplifier between the gate of the adjustment tube and the Miller capacitance, and the common-gate amplifier buffers the sampling of the Miller capacitance and feeds it back to the output terminal of the error amplifier to realize the The Le capacitor is isolated from the gate of the pass tube, so as to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More