Semiconductor device

A technology of semiconductors and transistors, which is applied in the field of semiconductor devices and can solve problems such as difficulties in the layout of NMOS transistors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 approach

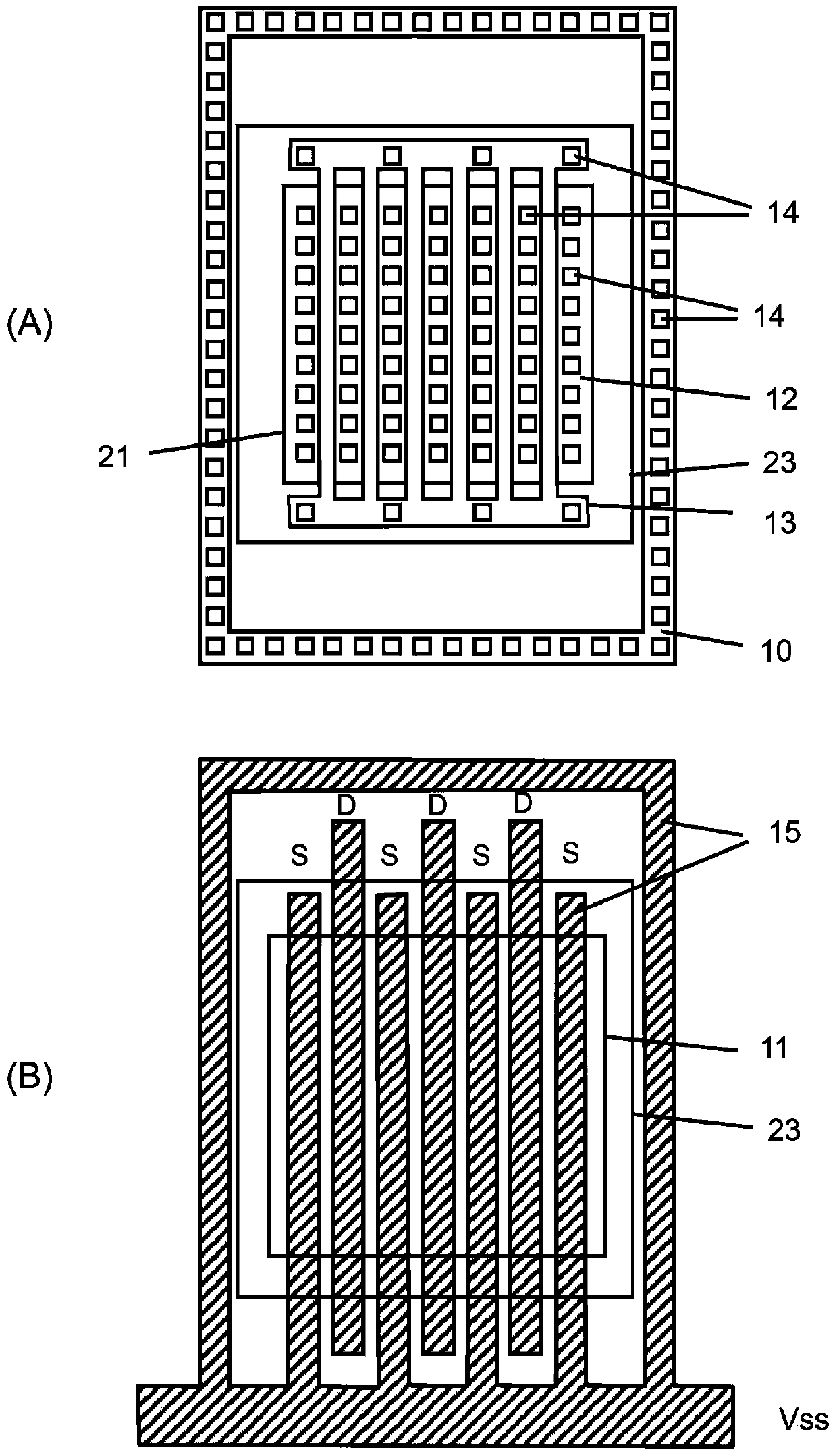

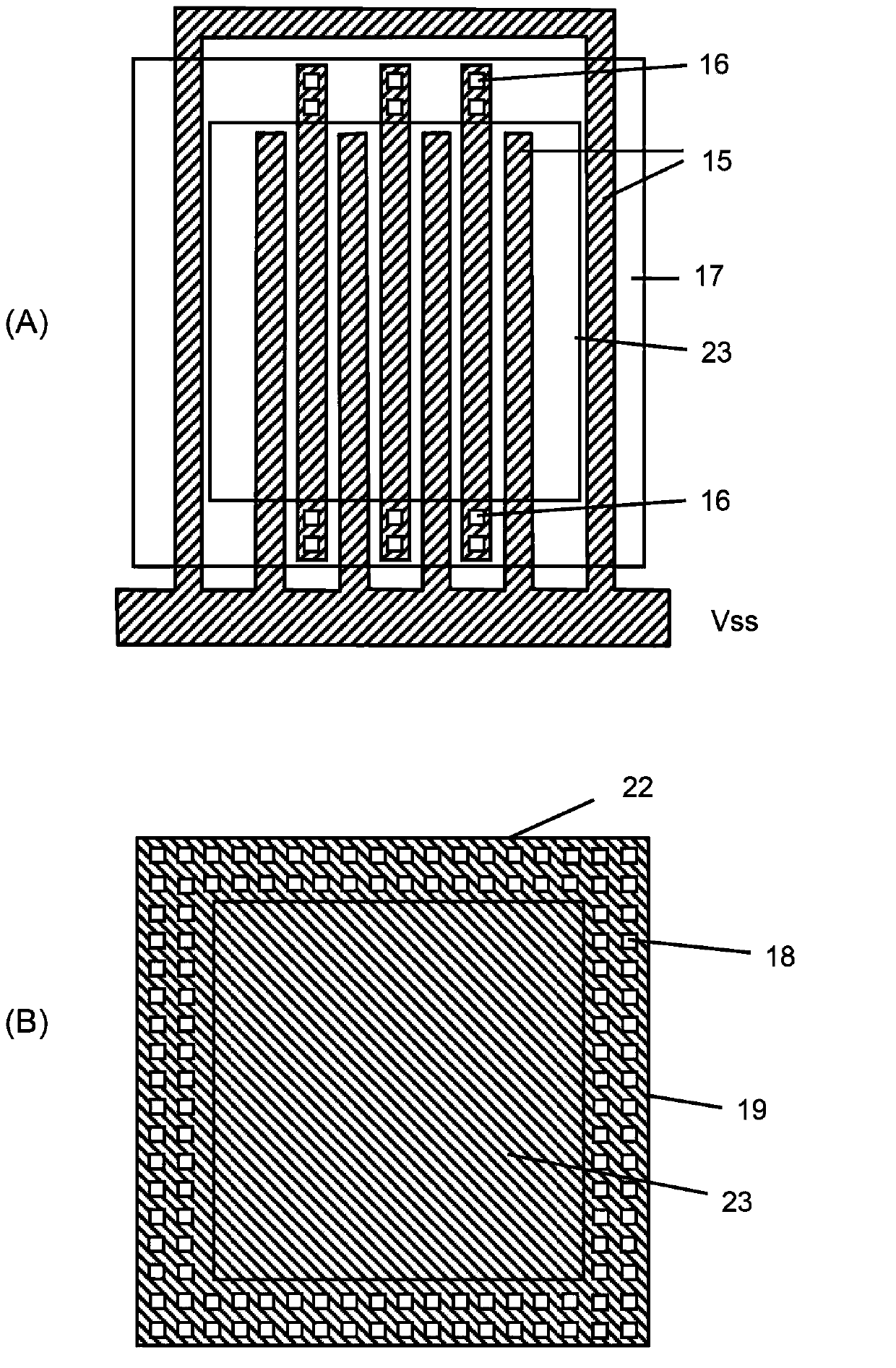

[0021] First, use figure 1 with figure 2 The pad structure of the semiconductor device will be described. figure 1 It is a plan view showing a pad structure of a semiconductor device, (A) shows a diffusion region, a gate electrode, a contact, and a pad opening, and (B) shows a diffusion region, an underlying metal film, and a pad opening. figure 2 is shown with figure 1 The top view of the pad structure of the same semiconductor device, (A) shows the lower metal film, the first via hole, the middle metal film and the pad opening, (B) shows the second via hole, the upper metal film and the pad opening. Disk opening.

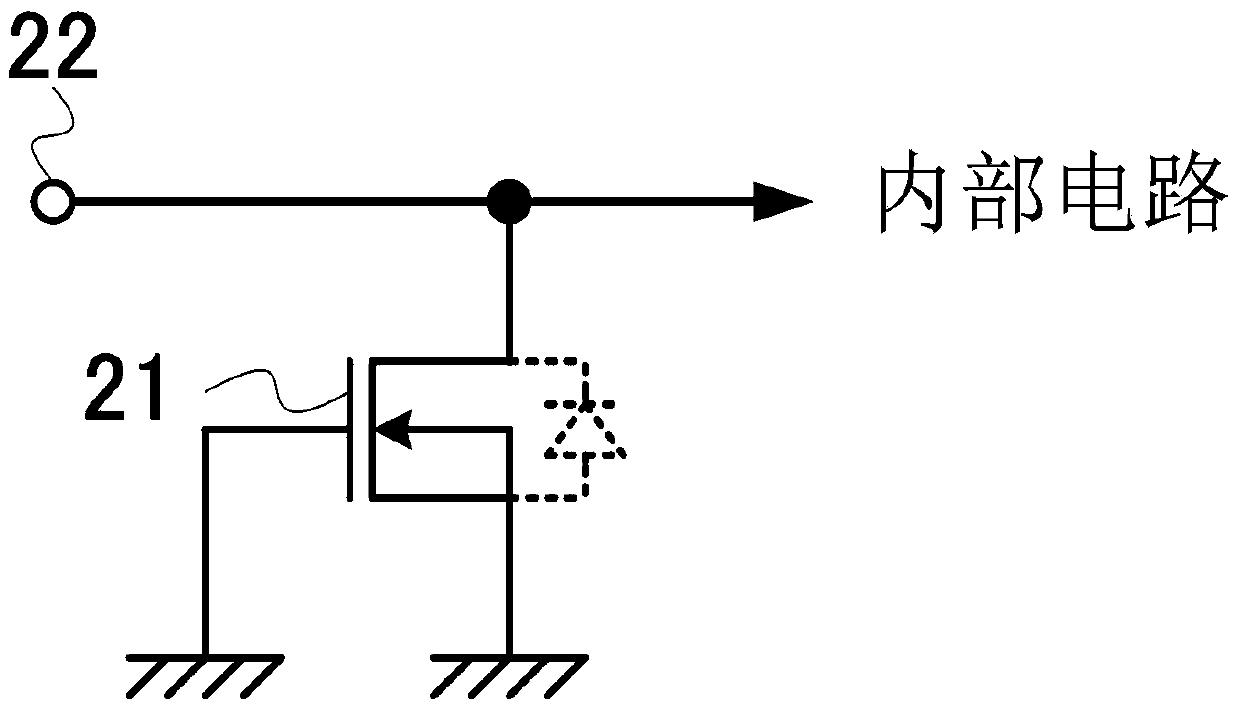

[0022] Such as figure 1 As shown in (A), a P-type diffusion region 10 for fixing the substrate potential and an N-type diffusion region 12 for the source and drain are provided, and a gate electrode is provided between the N-type diffusion regions 12 for the source and drain 13, constituting the NMOS transistor 21. The NMOS transistor 21 is a multi-finger ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More