Transistor capable of boosting electro-static discharge tolerance and its layout method

A technology of electrostatic discharge and layout method, which is applied in the direction of transistors, electric solid devices, circuits, etc., and can solve problems such as NSCR transistor 50 damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

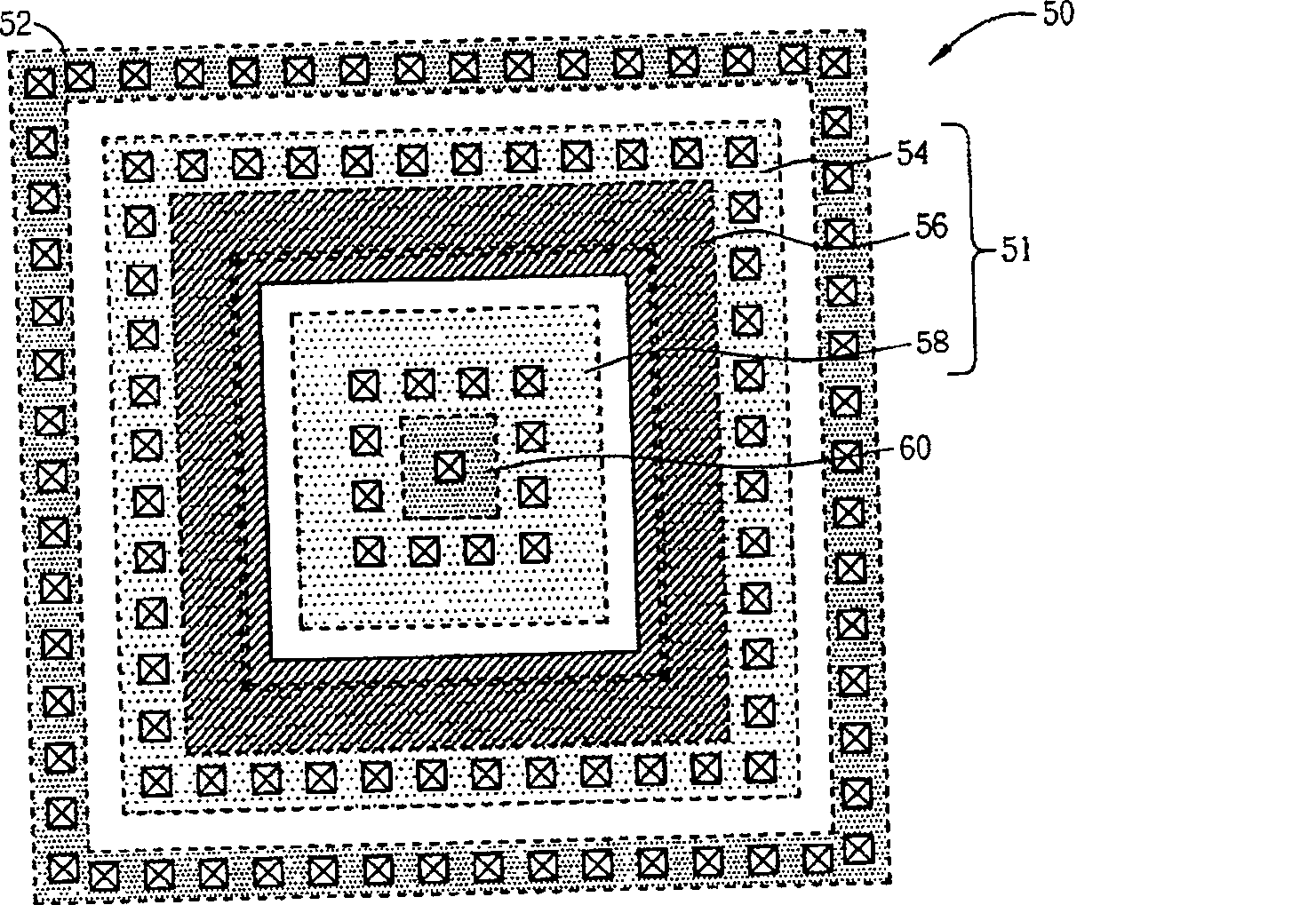

[0023] see Figure 4 , Figure 4 It is a schematic diagram of an embodiment of the NSCR transistor layout of the present invention. In this embodiment, the NSCR transistor 100 is a silicon-controlled rectifier (Silicon-Controlled Rectifiercell, SCR cell), which includes a Figure 4 The NMOS transistors 98A, 98B marked as 108, 112, 114, 104, and 106 are composed of a P-type semiconductor substrate (not shown), a P-type guard ring region 102, and two strip-shaped N-type diffusion Regions 104, 106, an annular N-type diffusion region 108, a P-type diffusion region 110, and polycrystalline regions 112, 114. In addition, the area surrounded by the dotted line frame 116 represents an N-type well wrapped in the ring-type N-type Below the diffusion region 108 , the P-type diffusion region 110 and part of the polycrystalline regions 112 and 114 . Depend on Figure 4 It can be seen that the contacts on the strip-shaped N-type diffusion regions 104, 106 and the P-type guard ring regio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More