Integrated circuit layout method based on best fit heuristic sequence and organizational evolutionary algorithms

An integrated circuit and heuristic technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as low layout efficiency, few heuristic guidance, and increased calculation time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

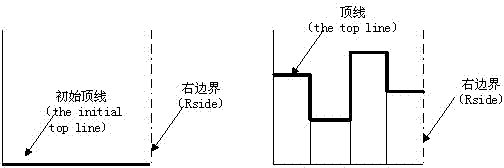

[0068] The VLSI layout problem studied in the present invention refers to placing all modules in the first quadrant when the optimal adaptation heuristic sequence requires that all modules are in the most suitable positions, and requiring them to be in the first quadrant. There is no overlap between them, and the area of the envelope surrounding all modules is minimized. There are many types of VLSI layout problems. The single-objective, soft rectangular module and the mixed VLSI layout problem of the soft rectangular module and the hard linear boundary module solved by the present invention aim to make the area utilization rate of the chip Optimal, and test the data sets of the two standard question banks MCNC and GSRC.

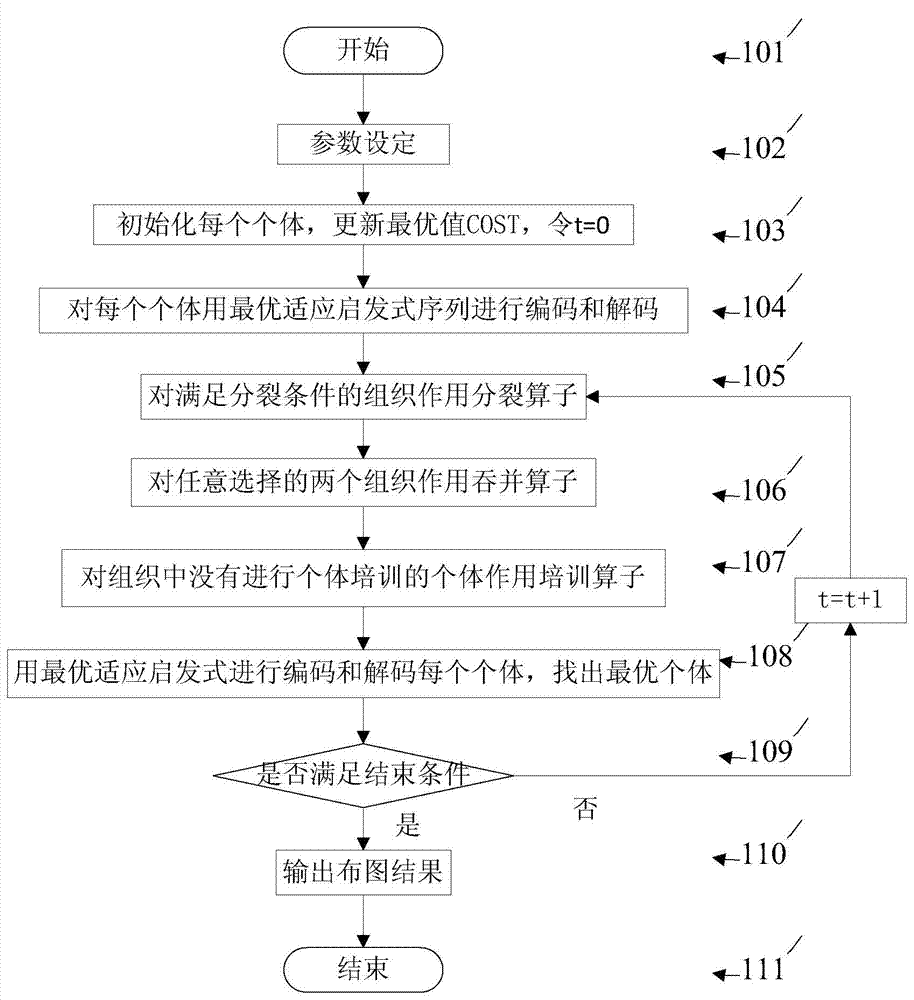

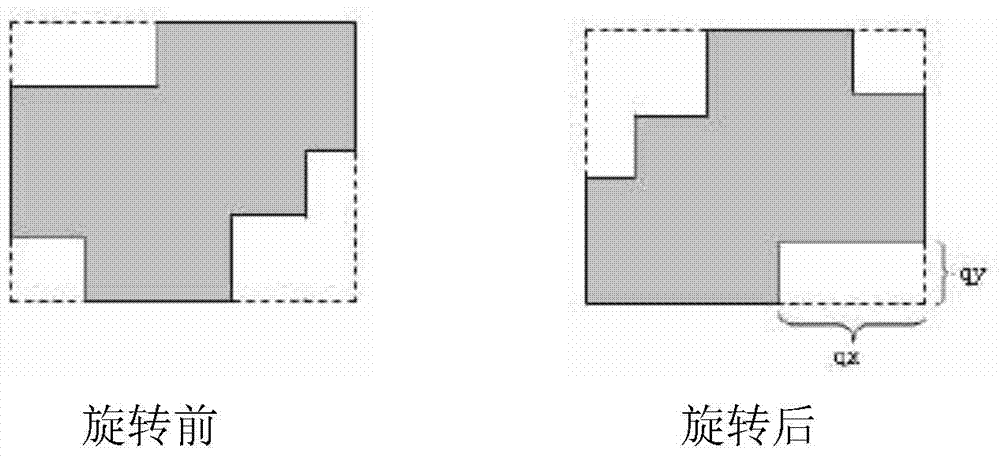

[0069] The present invention initializes each individual according to the characteristics of the module, and each individual contains three elements: BFHS, COST, and Treated (record whether the individual has been trained). Search whether each individual con...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More