Direct-current offset calibration method and circuit for pipelined analog-to-digital converters

An analog-to-digital converter, DC offset technology, applied in the direction of analog/digital conversion calibration/testing, etc., can solve the problems of increasing circuit complexity, affecting the accuracy and speed of the analog-to-digital converter, and improving the dynamic range and effective number of digits. , the effect of reducing DC offset and increasing flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

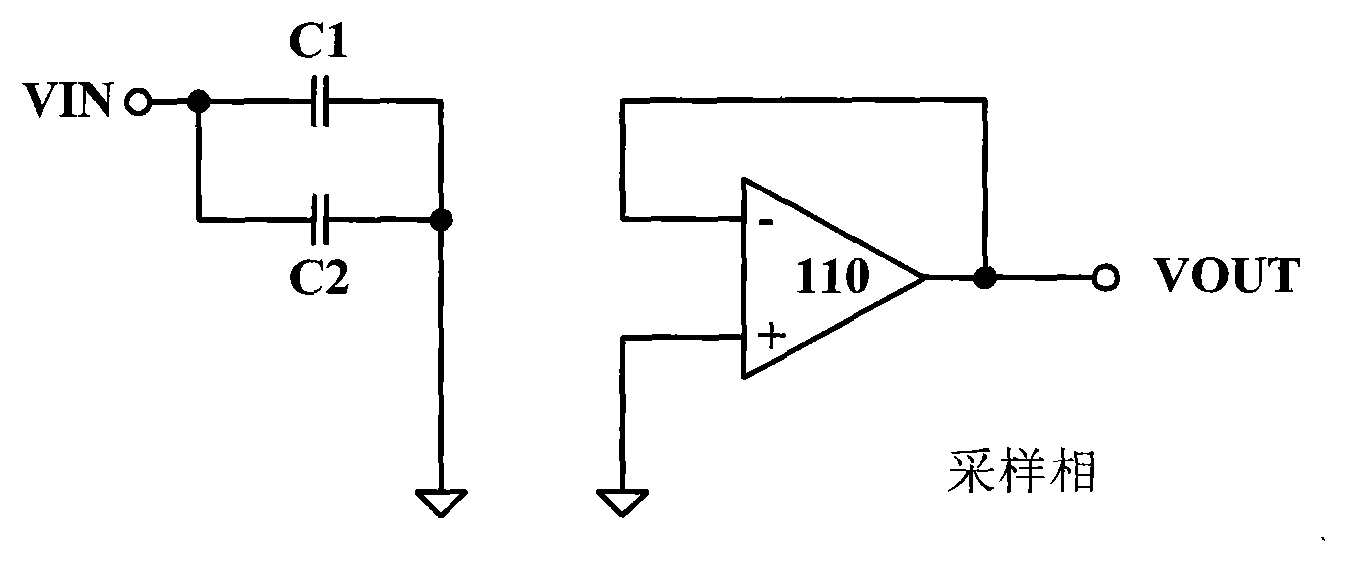

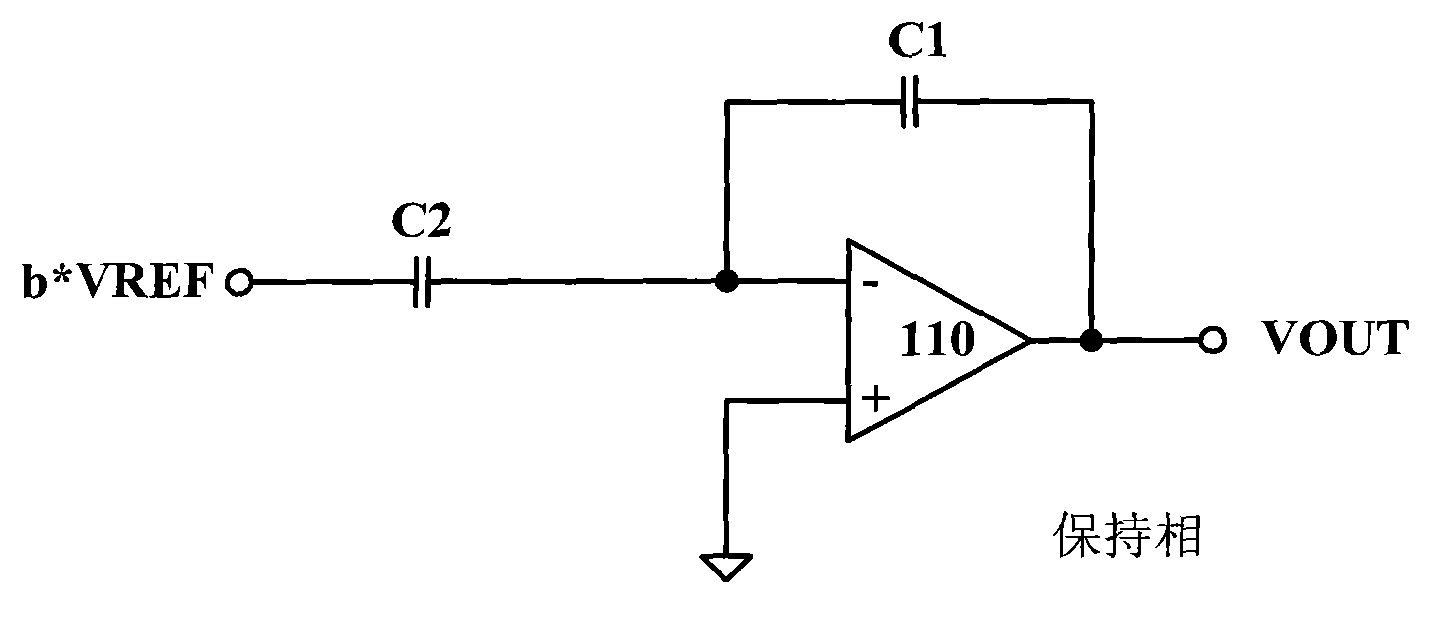

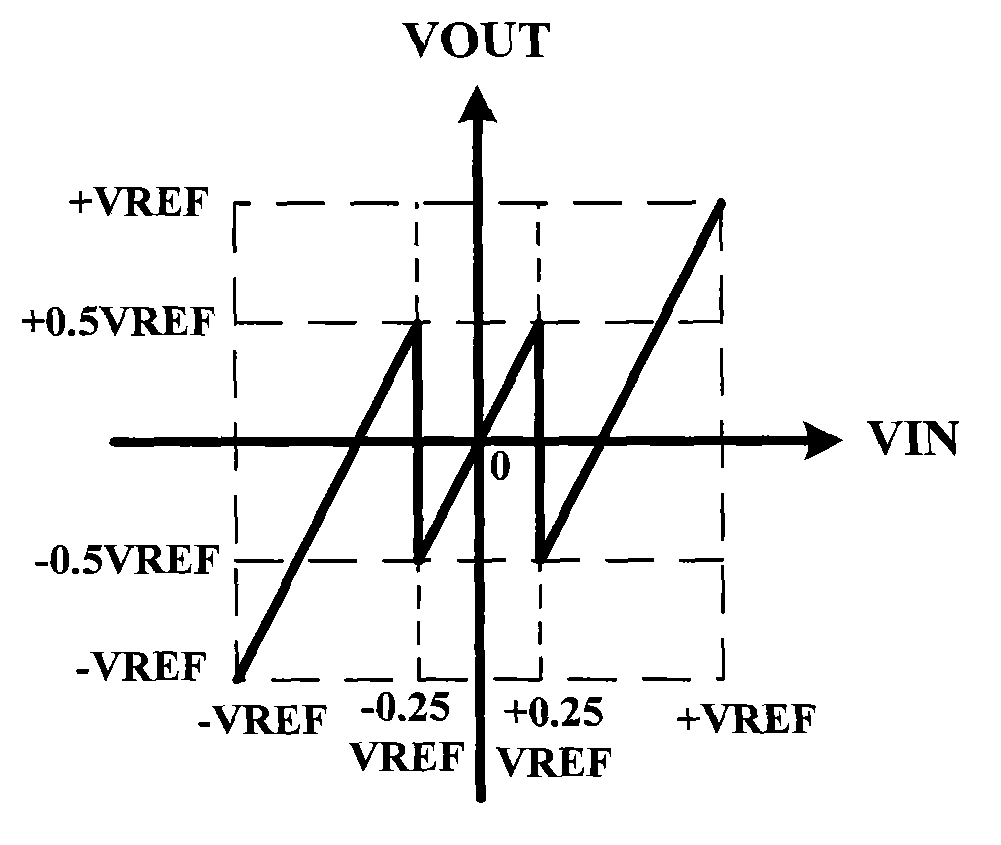

The specific embodiments of the present invention will be described below in conjunction with the accompanying drawings.

See Figure 8 As shown, the pipeline ADC core circuit 100 is an existing DC offset core circuit of an operational amplifier, and the DC offset calibration circuit 200 is a DC offset calibration circuit proposed by the present invention for pipeline AD converters. The implementation circuit of the algorithm includes a logic control module 210 , a calculation and storage module 220 and an asynchronous subtractor module 230 .

The above-mentioned logic control module 210 adopts the same operating clock CLOCK as the core circuit of the pipeline analog-to-digital converter; the input signal connected to it includes the calibration start enable signal START, and the calibration reset enable signal RESET; the output signal connected to it includes , calculation and storage enable signal ENABLE, analog-to-digital converter sampling switch control signal Input Short...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More