Method for calculating contact pressure between grinding pad and surface of chip in CMP simulation model

A technology of contact pressure and calculation method, which is applied in the fields of calculation, instrumentation, electrical and digital data processing, etc., can solve the problems of lack of CMP model realization technology, and achieve the effect of generality and versatility, and improving the calculation speed.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

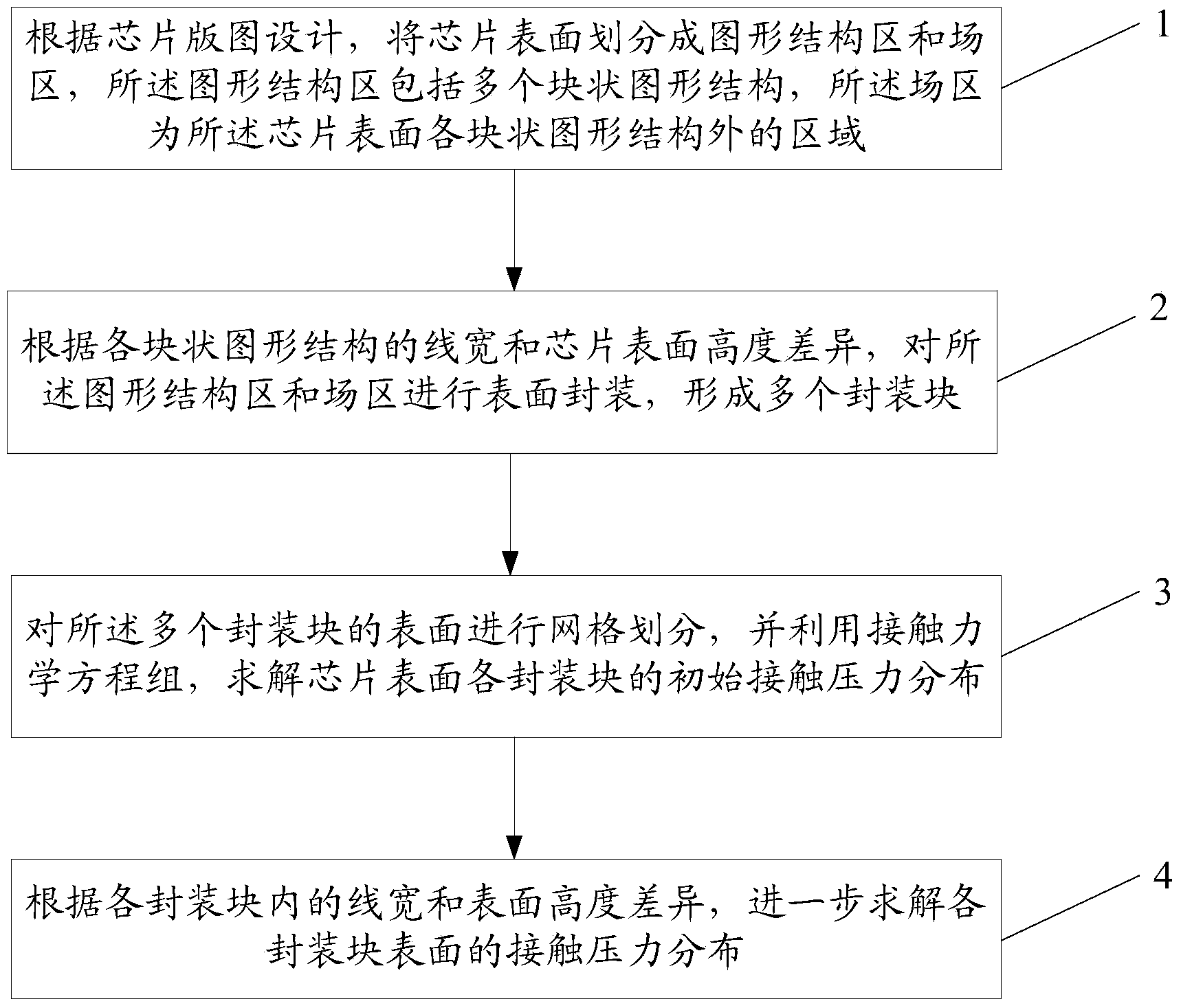

[0065] Such as figure 1 As shown, the embodiment of the present invention provides a calculation method of the contact pressure between the polishing pad and the chip surface in a CMP simulation model, including:

[0066] Step 1: Divide the chip surface into a graphic structure area and a field area according to the chip layout design, the graphic structure area includes a plurality of block graphic structures, and the field area is the area outside each block graphic structure on the chip surface .

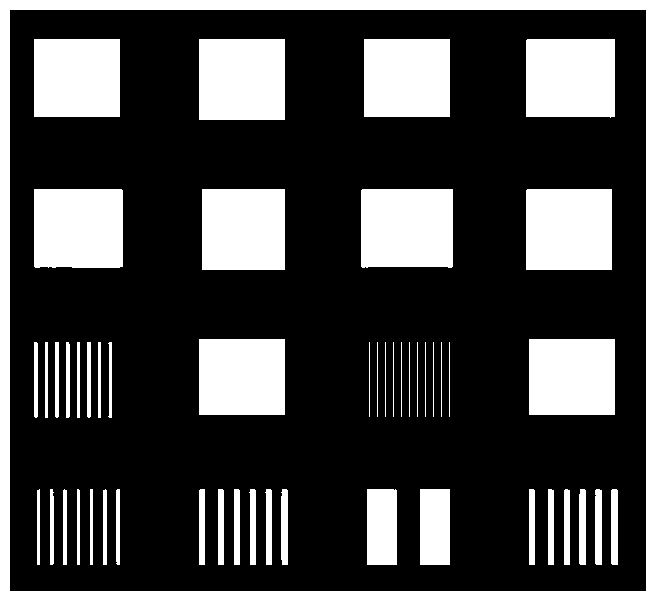

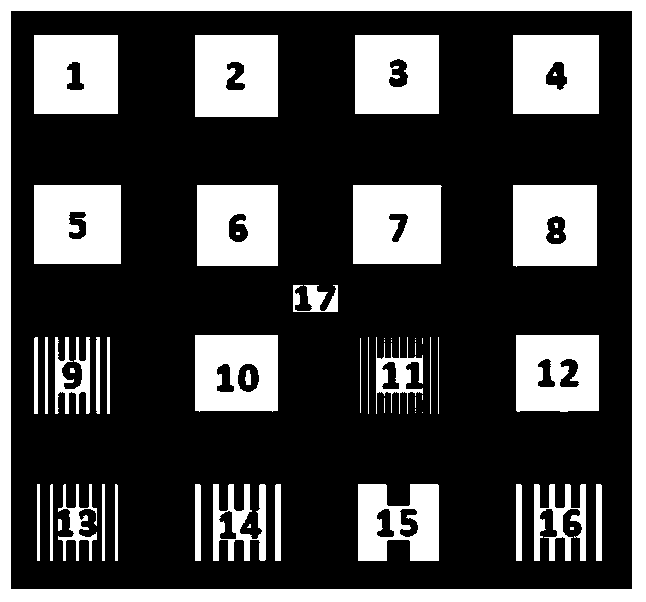

[0067] Take a 2cm*2cm chip as an example, such as figure 2 As shown, according to the chip layout design, the chip surface is divided into a pattern structure area and a field area, and the pattern structure area includes a plurality of block pattern structures, and the field area refers to figure 2 The black area on the surface of the middle chip except for each block pattern structure.

[0068] Step 2: according to the difference in line width and chip surface height of ea...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More