Rising edge detection circuit

A one-way, transistor technology, applied in the field of rising edge detection circuit, can solve problems such as unsatisfactory, and achieve the effect of simple structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

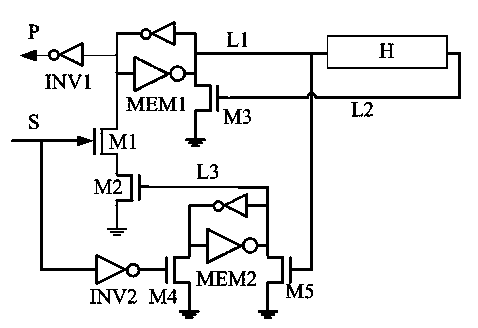

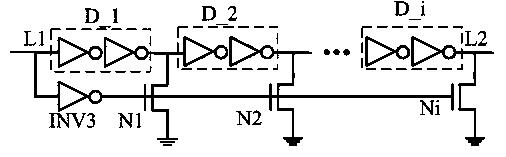

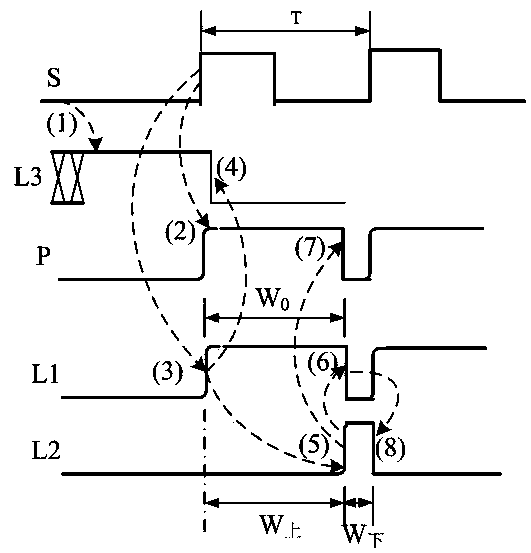

[0010] The specific implementation manner of the present invention will be described below with reference to the accompanying drawings. The basic structure of the present invention is as figure 1 As shown: an input terminal S and an output terminal P are provided, the input terminal S is connected to the gate of the NMOS transistor M1, the source of the NMOS transistor M1 is connected to the drain of the NMOS transistor M2, and the source of the NMOS transistor M2 Grounded, the drain of the NMOS transistor M1 is connected to the bistable memory unit MEM1 one way, and the other is connected to the output terminal P through the inverter INV1; the other end (L1 end) of the bistable memory unit MEM1 is connected to the NMOS transistor The drain of M3 is connected, and the other channel is connected to the gate of NMOS transistor M3 through an asymmetric delay circuit H (the output terminal of asymmetric delay circuit H is L2), and the source of NMOS transistor M3 is grounded; An ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More