On-package multiprocessor ground-referenced single-ended interconnect

A processor, single-ended technology, applied in the direction of electrical digital data processing, instruments, static memory, etc., can solve the problems of low cost, chip signaling technology can not efficiently support multi-processing performance targets, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

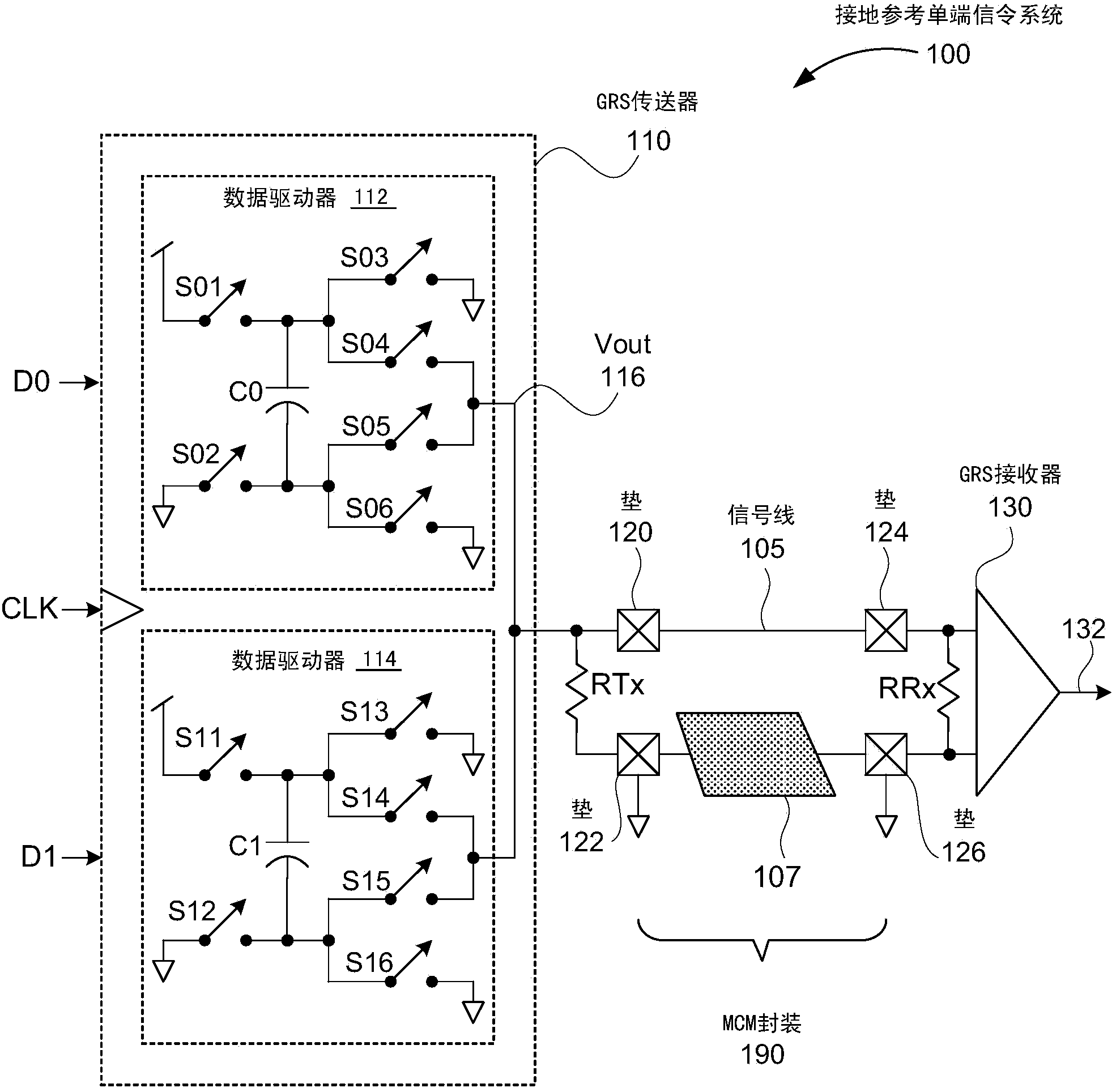

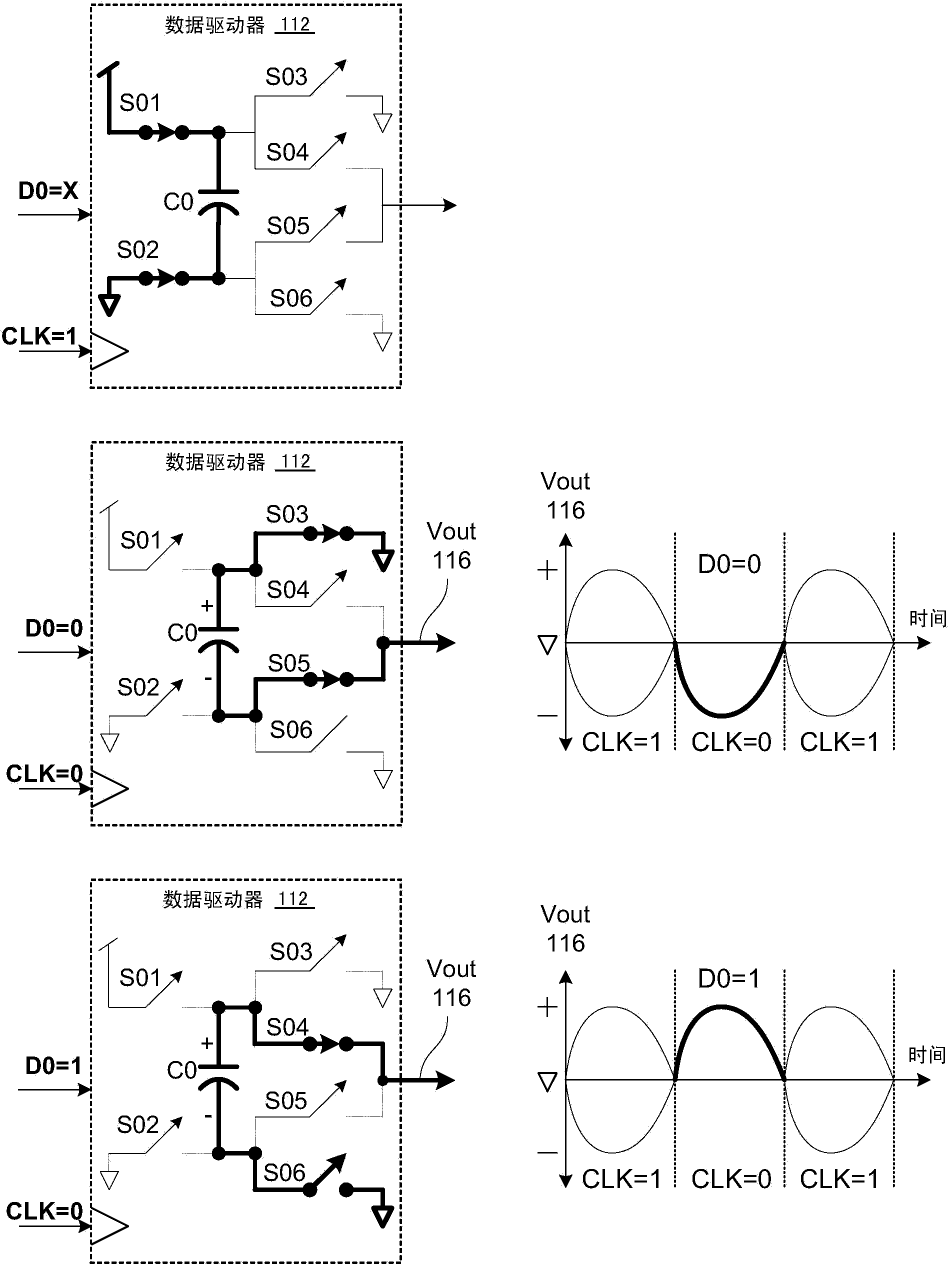

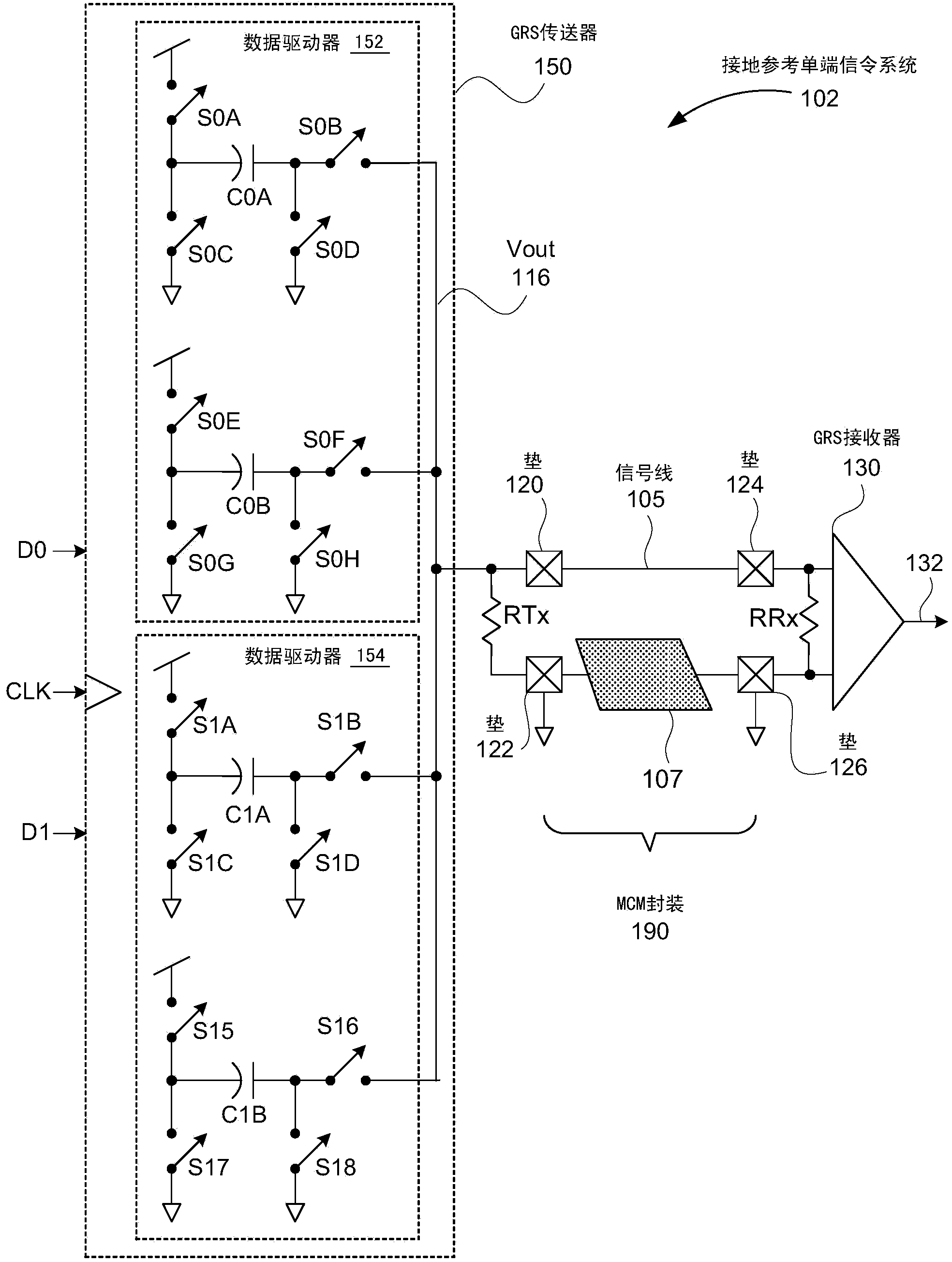

[0031] Techniques are provided for high-speed single-ended signaling between different chips making up a system-on-package device. The ground-referenced drivers deliver pulses with polarities determined by corresponding logic states. The pulses traverse the signal path and are received by a ground-referenced amplifier, which amplifies the pulses for interpretation as conventional logic signals. A set of ground-referenced drivers and ground-referenced amplifiers implement a high-speed interface configured to interconnect different chips making up a system-on-package device. The high speed communication enabled by ground reference signaling advantageously improves the bandwidth between different chips within a system-on-package device, which enables higher performance and higher density systems than provided by conventional signaling techniques .

[0032] Embodiments of the invention implement a system that includes a plurality of different processor chips, one or more memory ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More