Log-likelihood ratio (LLR) dampening in low-density parity-check (LDPC) decoders

A logarithmic likelihood ratio and damping technology, which is applied to the application of multi-bit parity bit error detection coding, coding, instruments, etc., can solve the problem of reducing the storage capacity of NVM

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

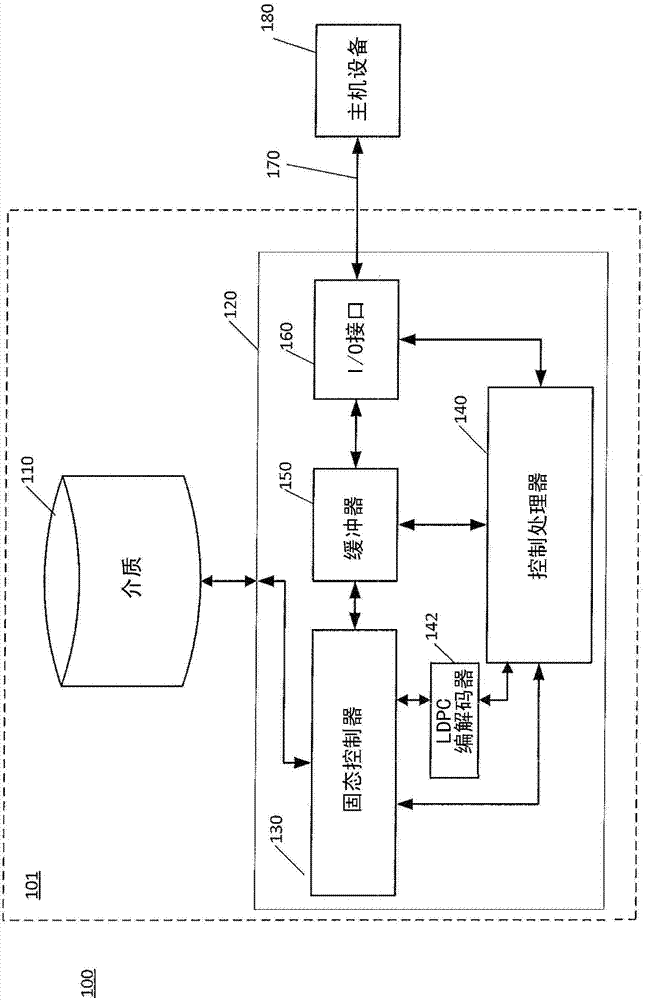

[0024] The described embodiments provide a media controller that reads data stored in the media. The media controller determines the value of each bit of the shortened codeword from the media. The shortened codeword comprises a plurality of non-shortened bits of a full codeword, wherein the full codeword comprises a plurality of non-shortened bits and one or more shortened bits. The shortened bits correspond to unused bits in the shortened codeword. The media controller converts the determined value of each bit of the shortened codeword into a first set of log-likelihood ratio (LLR) values. The full codeword is decoded using the first set of LLR values of the shortened codeword. The media controller dampens one or more LLR values corresponding to the non-shortened bits of the codeword to generate a second set of LLR values, and decodes the second set of LLR values.

[0025] Table 1 defines a list of acronyms used throughout this specification to aid in understanding the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More