Technological mapping method and integrated circuit for optimizing register control signal

A control signal and process mapping technology, applied in the field of process mapping, can solve the problems of scattered control signals, loose layout results, and large complexity, and achieves the effect of optimizing register control signals and improving the success rate.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] figure 1 It is a flowchart of a process mapping method for optimizing register control signals in the present invention. The method includes the following steps:

[0018] In step 100, register-transfer-level synthesis is performed on the user design to obtain a gate-level netlist of registers. RTL (Register-transfer Level), that is, the register transfer level, there is a direct mapping relationship between the statements in the RTL model writing and the actual register structure model, and the register transfer level synthesis is to map the RTL writing to specific devices to achieve equivalence The function of the gate-level netlist is to realize the function of RTL under the specific process (such as smic0.13um logic G) of specific devices (such as standard cells). For example, in RTL, Y=A+C; then in the gate-level netlist, it will become: there is a standard unit OR2X2 under smic0.13um logic G, its input is A, C, and its output is Y.

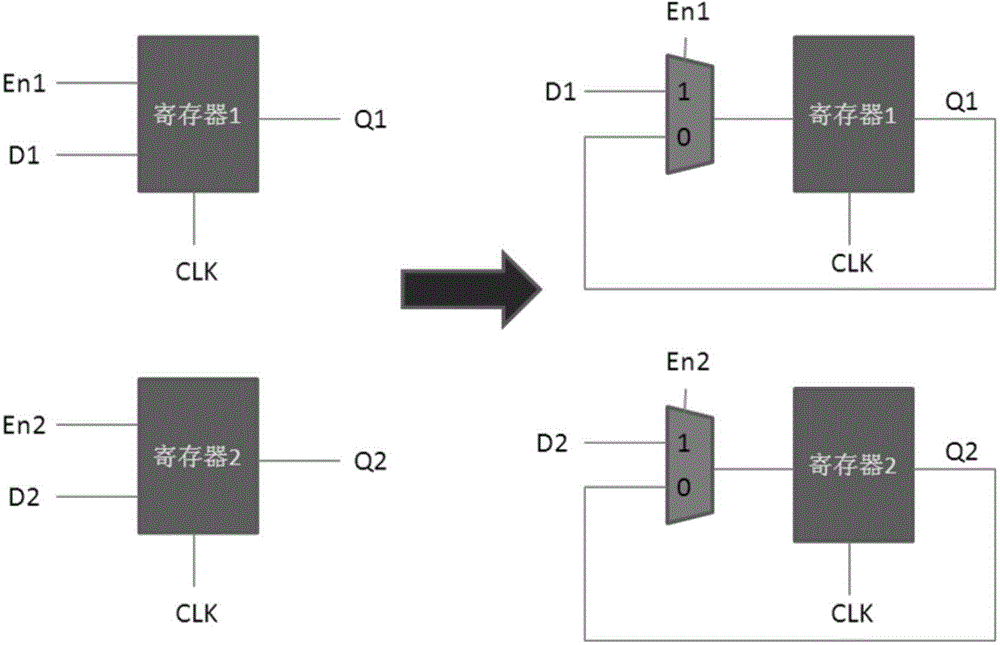

[0019] In step 101, the cont...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More