Method for double-sided polishing of semiconductor wafer

A double-sided polishing, semiconductor technology, used in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as increasing the risk of carrier warpage, reducing the moment of inertia, and damaging installation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

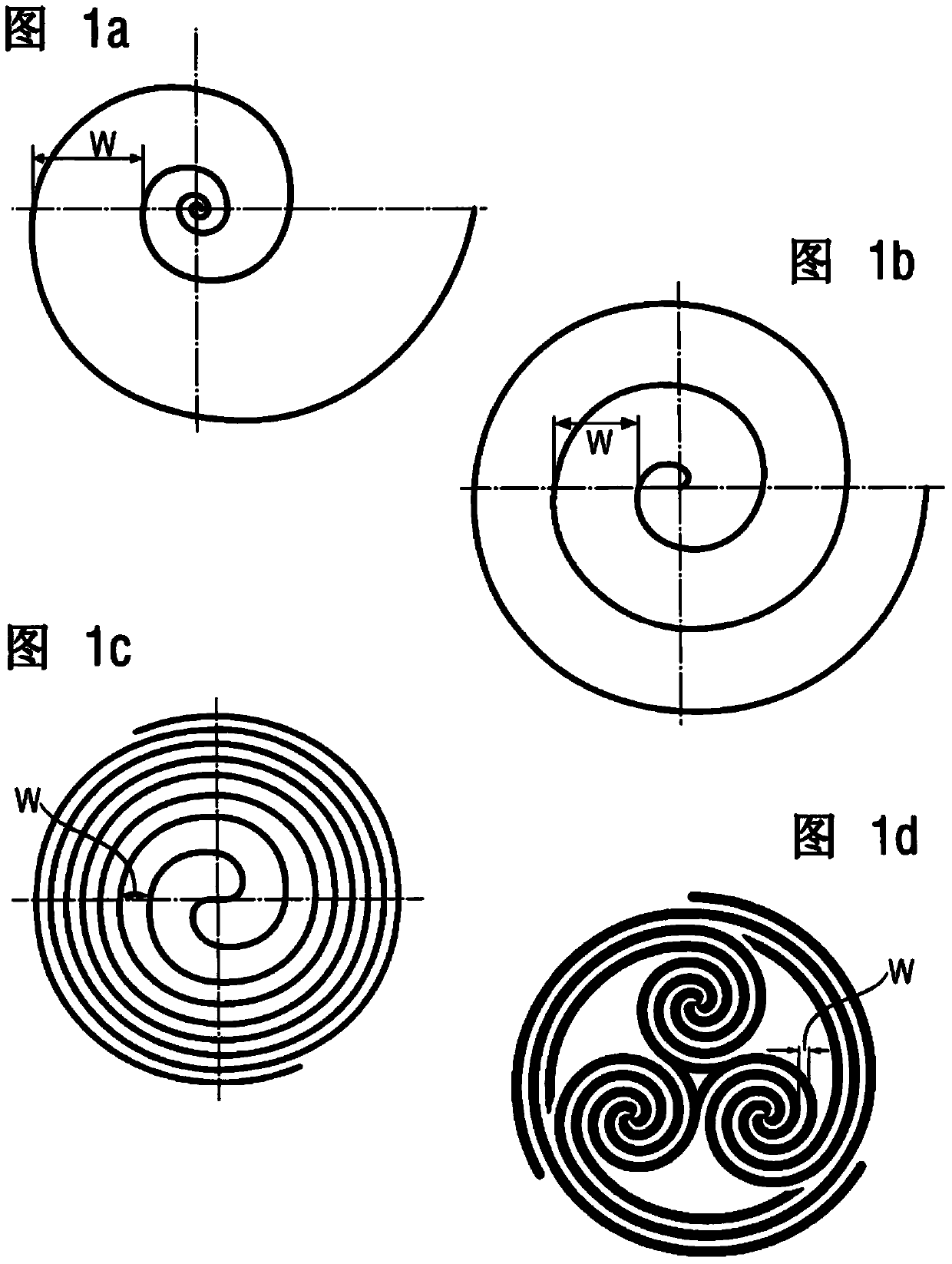

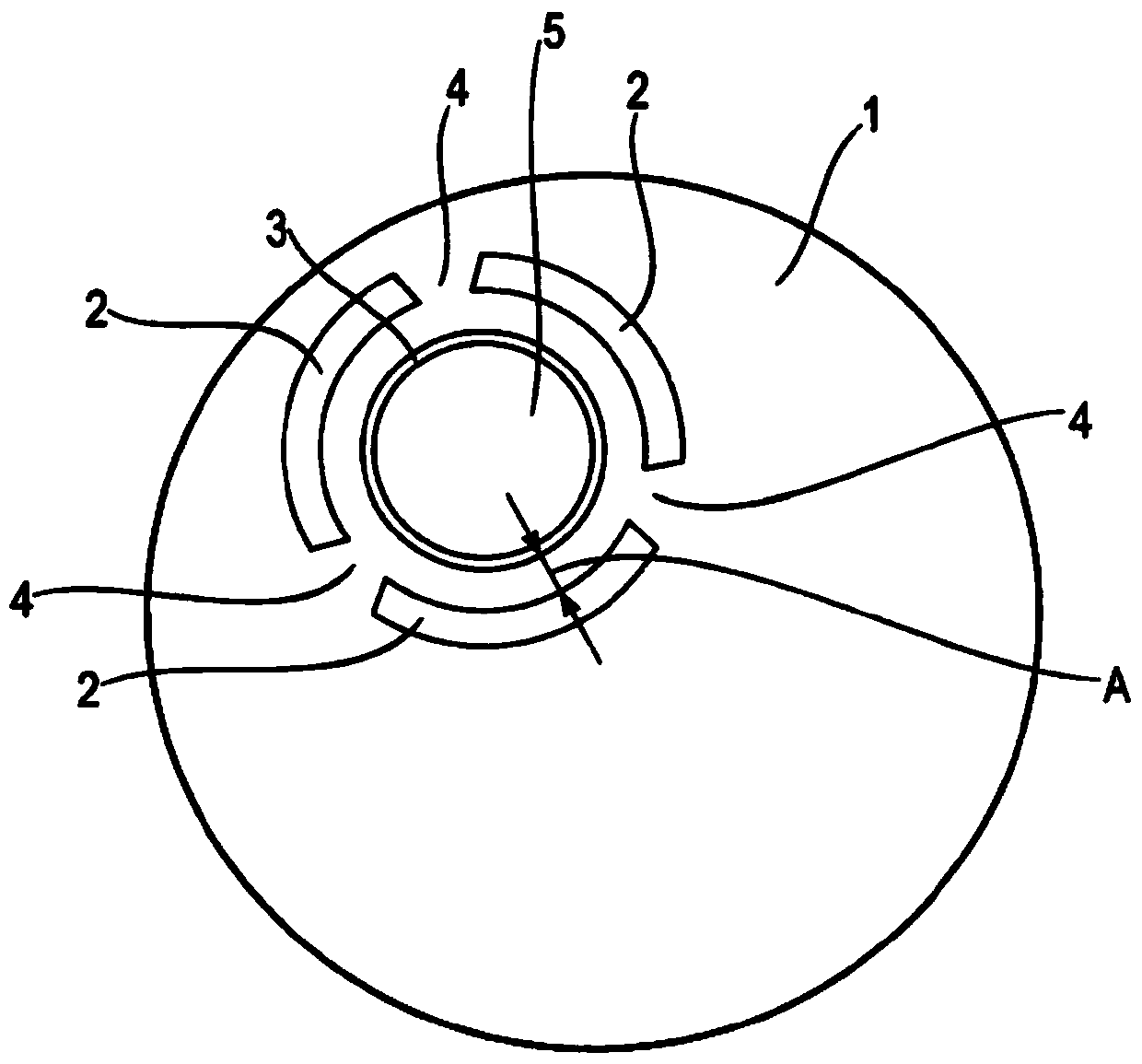

[0034] The inventive method includes not only local aspects limited to specific technical components or individual method-technical features (eg individual method parameters), but also related method features. These method characteristics are grouped into:

[0035] 1) Polishing pads with a specific surface structure,

[0036] 2) Reconstruction of the carrier board used to accommodate the wafer, and

[0037] 3) Supply of polish on both sides.

[0038]In the inventive method for simultaneous double-sided polishing (DSP) of wafers made of semiconductor material, a silica sol according to the prior art is used as polishing agent, said silica sol comprising particles with a size of 20-50 nm A slurry of colloidally distributed particles.

[0039] The distribution of the polishing agent in the DSP process is influenced by, among other things, the properties of the polishing pad surface (working surface) which is in material-removing contact with the front and / or back side of the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More