Design method for preventing upper MOS of VR from being broken down to burn up CPU

A design method, P12V technology, applied in the protection of under-voltage or no-voltage, data processing power supply, etc., can solve the problems of burning the CPU, burning the CPU, and using it for a long time.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

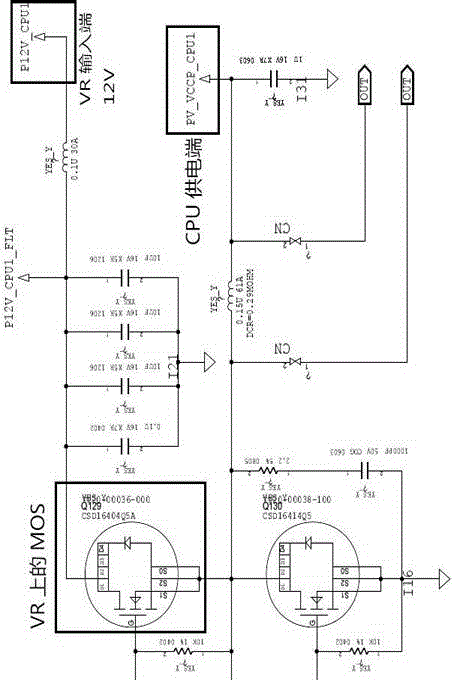

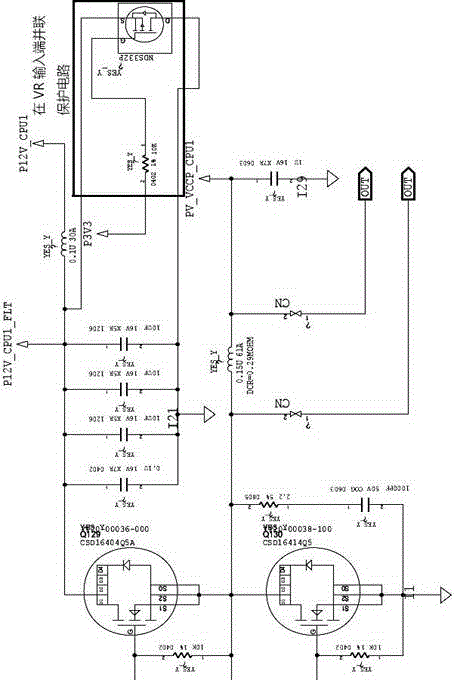

[0011] Refer to the attached figure 1 , 2 , the present invention is further described by means of specific embodiments:

[0012] like figure 1 The schematic diagram of the VR principle before improvement is shown: it can be seen that if the upper MOS of VR is broken down, P12V_CPU0 will be directly connected to PV_VCCP_CPU0 through the upper MOS, and PV_VCCP_CPU0 is the power supply of the CPU, so once the upper MOS is hit wear, it is equivalent to the CPU directly connected to 12V, causing MOS to burn;

[0013] like figure 2 Shown is the improved design method (that is, proposed in this paper), which is realized by adding a PMOS at both ends of the input capacitor; in this way, when the upper MOS of VR breaks down, the voltage at both ends of the input capacitor will decrease, once The reduced voltage value is less than 3.3V (if the G electrode voltage is set higher, the trigger will be earlier), the VGS of the PMOS is less than 0, the PMOS will be turned on, and P12V_C...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com