Method for removing intersymbol interference and decision feedback sequence predicator

An inter-symbol crosstalk and decision feedback technology, applied in the field of decision feedback sequence predictors, can solve the problems of chip design risks, the overall performance of 1000BASE-T physical layer chips cannot be fully verified by FPGA, and hidden dangers.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0080] The technical solutions in this embodiment will be clearly and completely described below with reference to the drawings in this embodiment. Obviously, the described embodiments are only a part of the embodiments of the present invention, but not all of the embodiments. Based on the embodiments of the present invention, all other embodiments obtained by those of ordinary skill in the art without creative efforts shall fall within the protection scope of the present invention.

[0081] In order to solve the problem in the prior art that the traditional decision feedback sequence predictor (DFSE) cannot run in the FPGA because its critical path is too long, and thus the overall performance of the 1000BASE-T physical layer chip cannot be fully verified by the FPGA. Chip design brings huge risks and hidden dangers. The present invention provides a novel decision feedback sequence predictor.

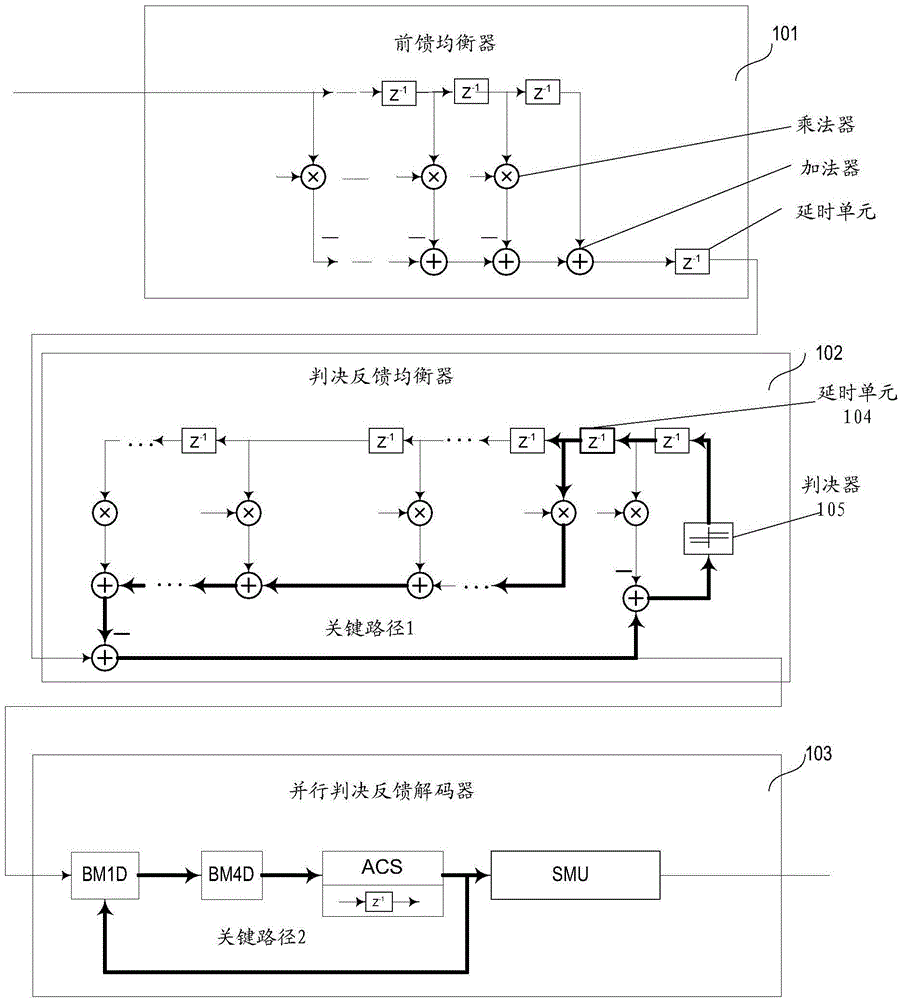

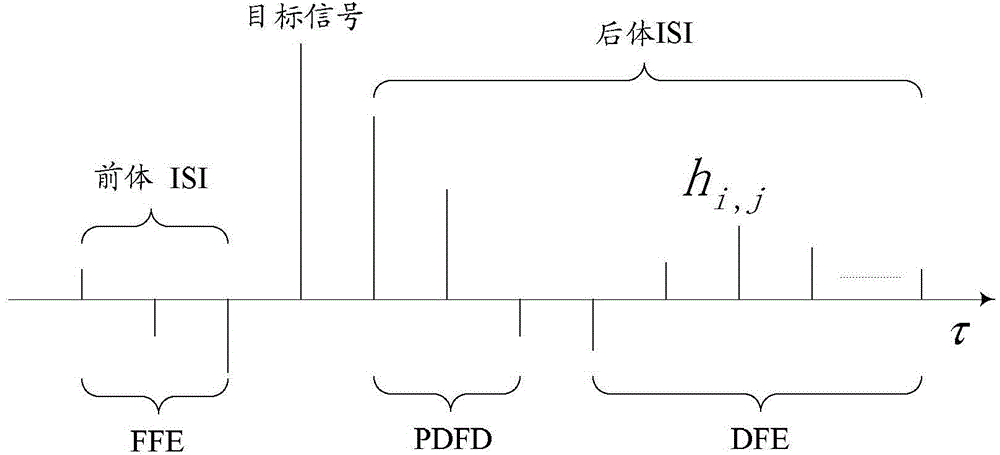

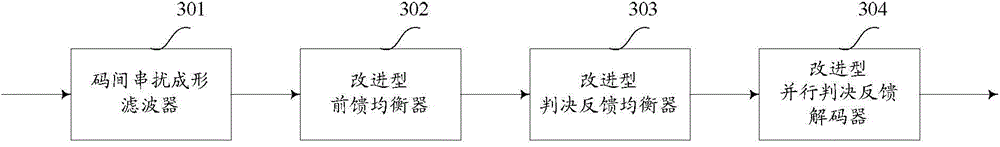

[0082] The DFSE provided by this embodiment includes an intersymbol interference s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More