Method of manufacturing semiconductor chip, semiconductor chip, and semiconductor device

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as low impact resistance, low chip flexural strength, and longer cutting time, and achieve high productivity effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0060] Hereinafter, embodiments of the present invention will be described with reference to the drawings.

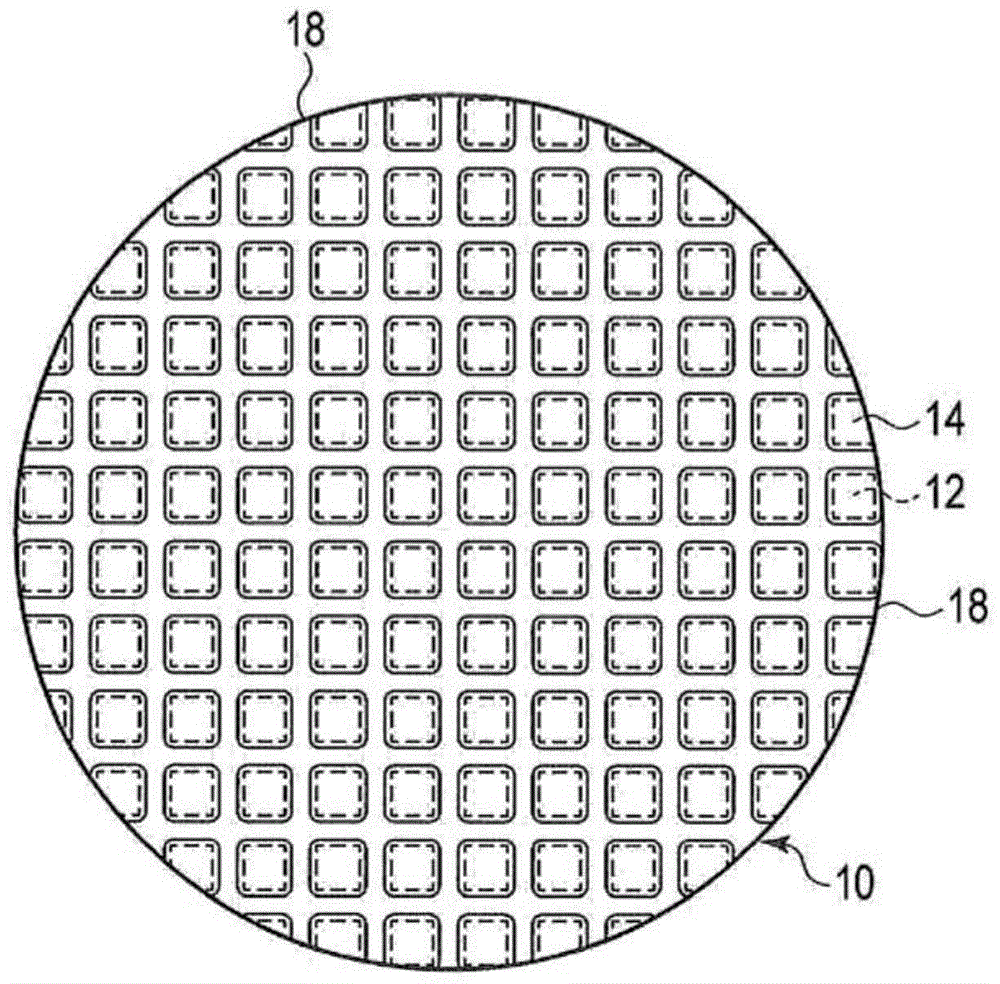

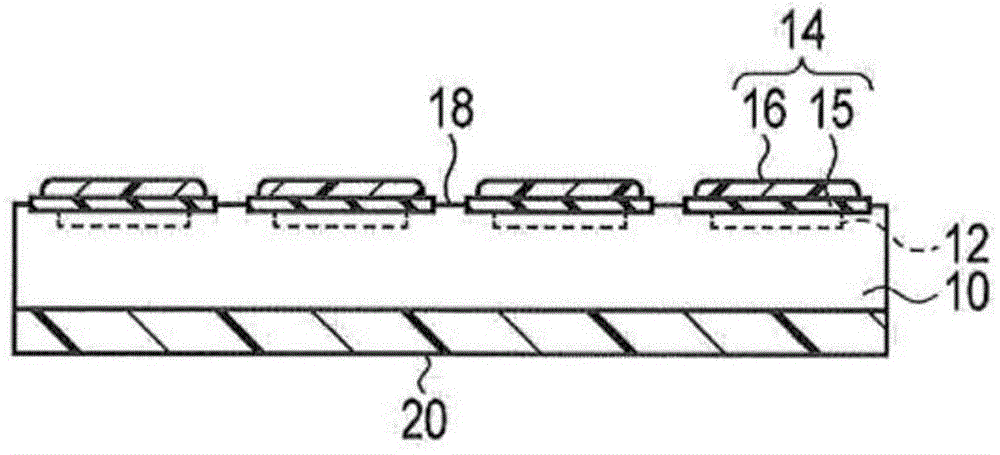

[0061] figure 1 It is a top view of a semiconductor substrate used in the method of one embodiment. figure 2 express figure 1 A partial cross-sectional view of a semiconductor device.

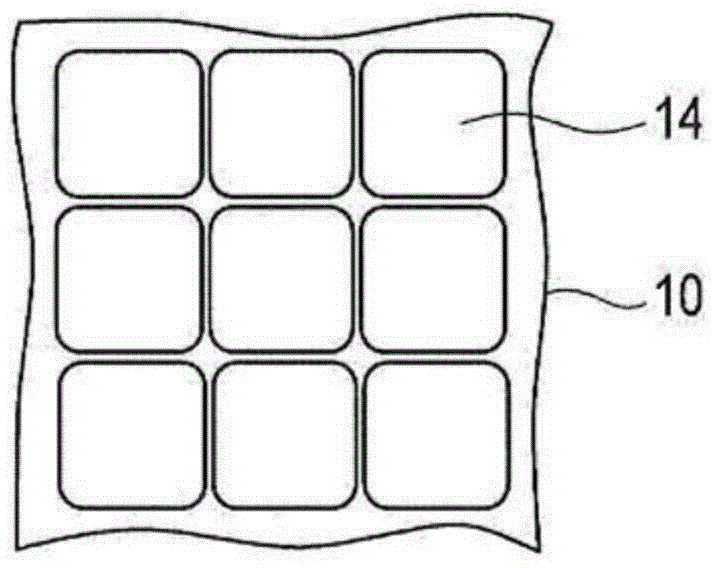

[0062] As shown in the figure, a plurality of element regions 12 are provided on a semiconductor substrate 10, and each element region 12 includes one or more semiconductor elements. These element regions 12 are arranged separately from each other. Each element region 12 is covered and protected by an etching mask 14 .

[0063] The semiconductor elements included in the element region 12 are, for example, transistors, diodes, light emitting diodes, or semiconductor lasers. The element region 12 may further include capacitors, wiring, and the like.

[0064]A region between adjacent element regions 12 is an exposed region 18 where the surface of the semiconductor substrate 10 is exp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com