Hardware implementation method and system for FEC in OTN system

A high-throughput, hardware-implemented technology, applied in transmission systems, digital transmission systems, and source coding adjustments, can solve problems such as the inability to meet FEC encoder throughput requirements, large-scale implementation, and waste of hardware resources. throughput, realize small scale, and save hardware resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0047] The present invention will be described in further detail below in conjunction with the accompanying drawings and embodiments.

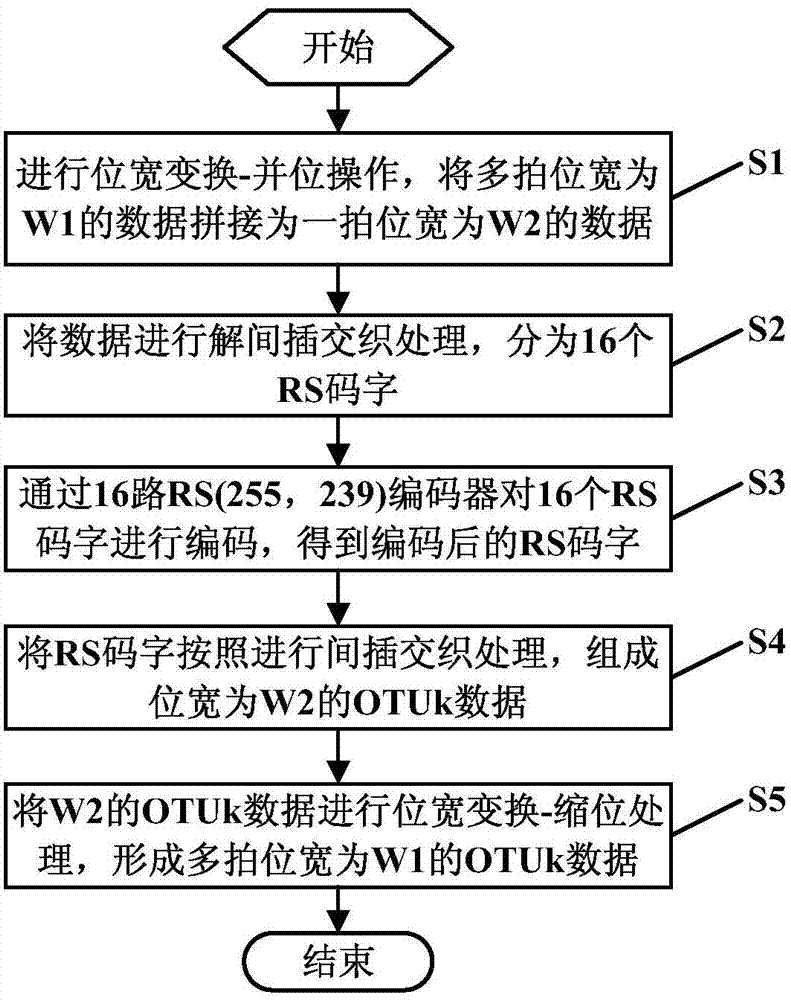

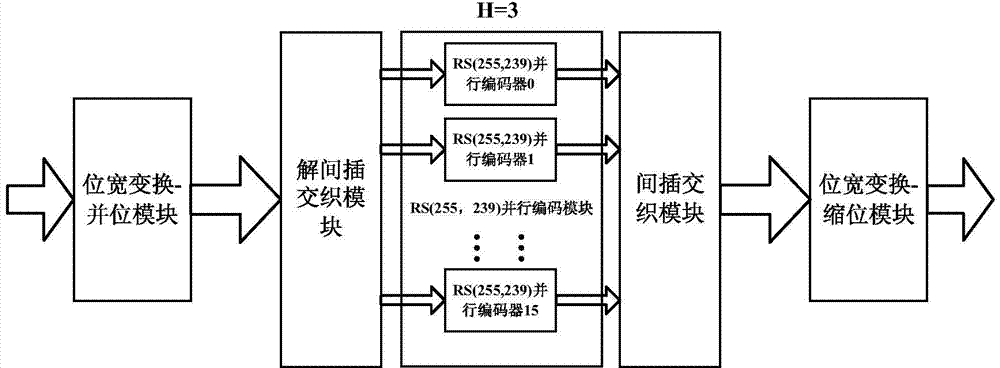

[0048] see figure 2 As shown, the hardware implementation method of the high-throughput FEC encoder in the OTN system in the embodiment of the present invention includes the following steps:

[0049] S1: splicing together the multi-beat transmission data with a bit width of W1 input by the upstream module in the OTN system to form an integrated data with a bit width of W2. W1 is the bit width required for OTN system implementation, W2 is the bit width suitable for FEC encoder parallel implementation, W2>W1, W2 is an integer multiple of 128, W2=16·8·H, (H is RS(255, 239) The degree of parallelism of the encoder, H is an integer), go to step S2.

[0050] Since the bit width W1 of the transmitted data is the bit width realized by the entire OTN system, and W1 is not necessarily an integer multiple of 128, it is necessary to extend W1 to W2.

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More