Method and system for characterizing cells using input waveforms generated considering different circuit topologies

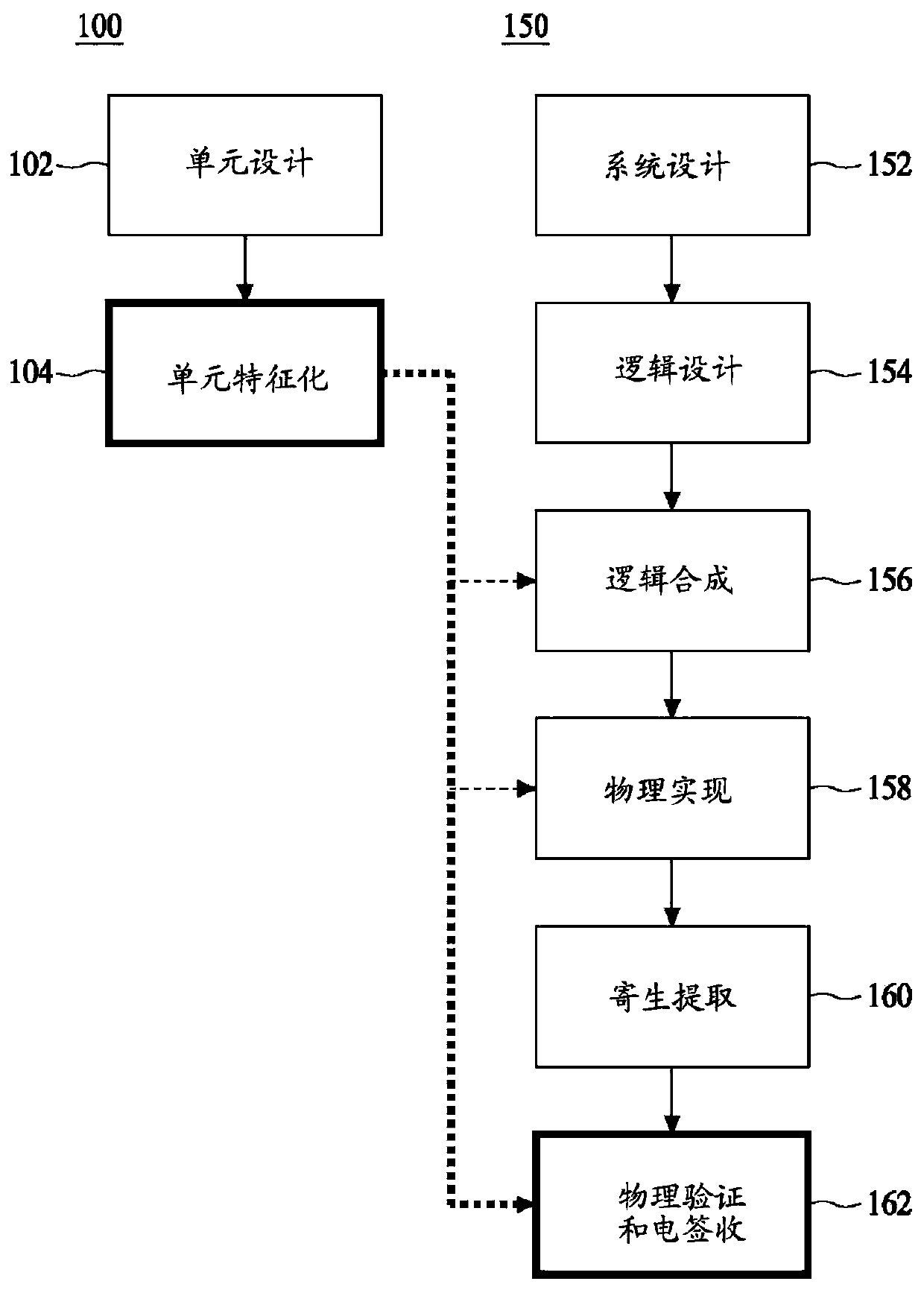

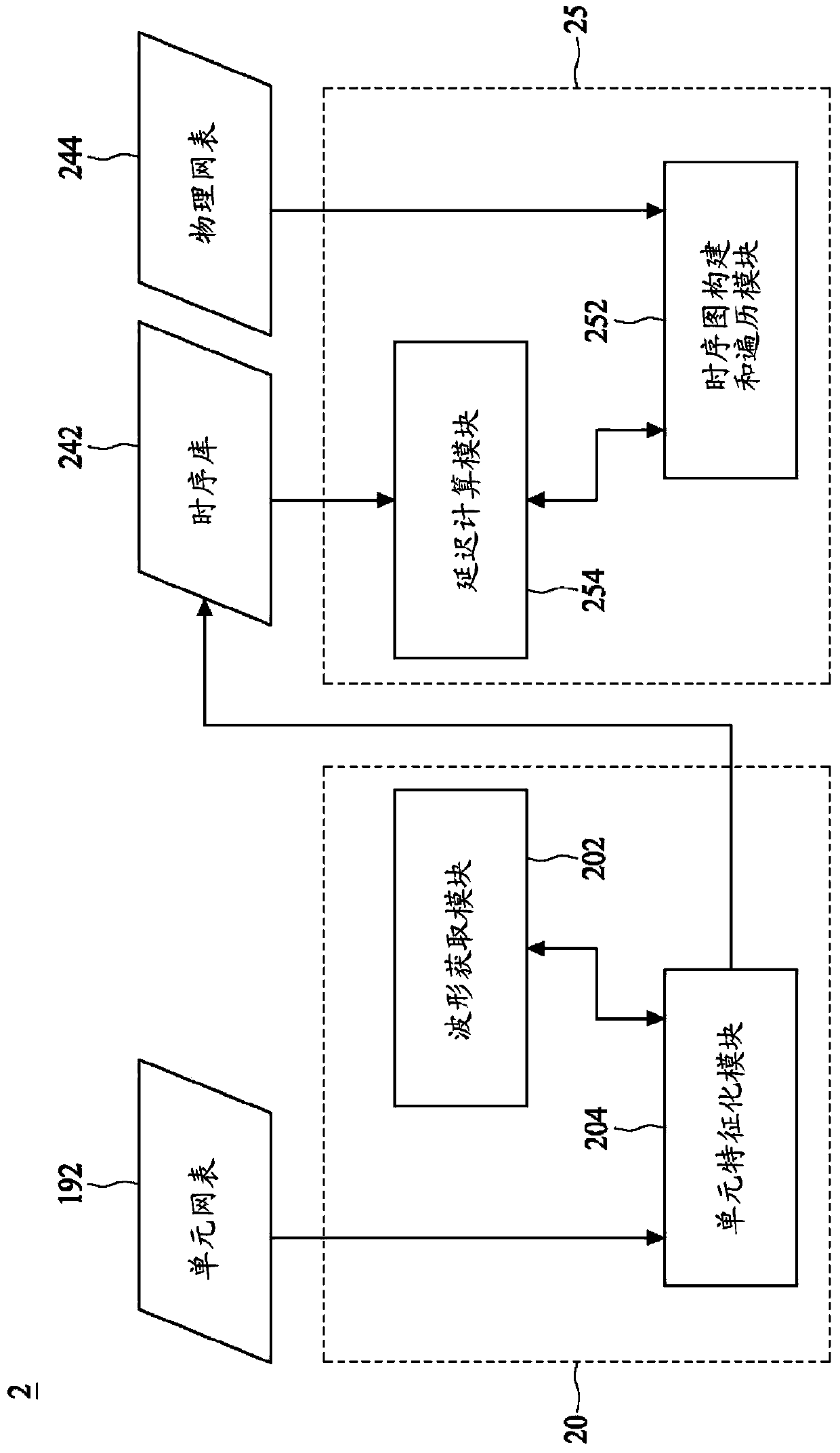

A circuit topology, input waveform technology, applied in CAD circuit design, electrical digital data processing, design optimization/simulation, etc., can solve the problems of delay calculation accuracy, distortion, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0056] Embodiments or examples of the invention illustrated in the drawings will now be described using specific language. It should be understood, however, that no limitation of the scope of the invention is intended. It is contemplated that any alterations and modifications in the described embodiments, and any further application of the principles described in this document would normally occur to one of ordinary skill in the art. Reference numerals may be repeated in all embodiments, but even if they share the same reference numeral, it is not necessarily required that features of one embodiment apply to another embodiment.

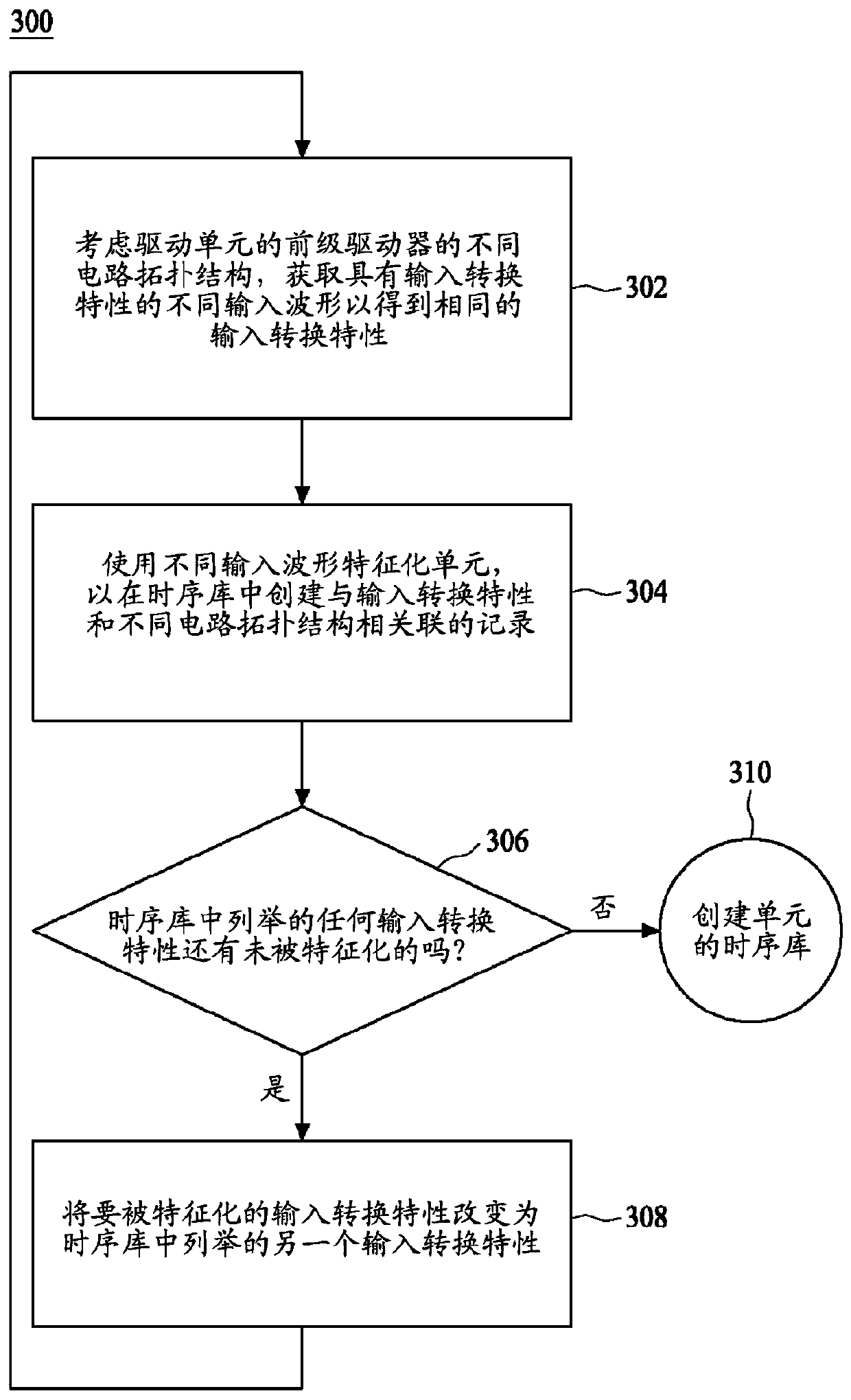

[0057] Some embodiments have one or a combination of the following features and / or advantages. In some embodiments, the cell is characterized according to the input transfer characteristic taking into account different circuit topologies of the pre-drivers of the driving cell to obtain the same input transfer characteristic. In some embodiments, the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More