Integrated circuit chip subjected to modularized packaging and manufacturing method thereof

A technology of integrated circuits and manufacturing methods, which is applied in the direction of circuits, electrical components, and electrical solid devices, can solve problems such as high cost of upgrading, failure to realize effective utilization of bare chips, and non-uniform interfaces of bare chips, and achieve convenient and reliable replacement. Good scope of application and low development risk

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The present invention will be described in detail below in terms of specific embodiments in conjunction with the accompanying drawings. The following examples will help those skilled in the art to further understand the present invention, but do not limit the present invention in any form. It is to be noted that other embodiments may be utilized or structural and functional modifications may be made to the embodiments set forth herein without departing from the scope and spirit of the invention.

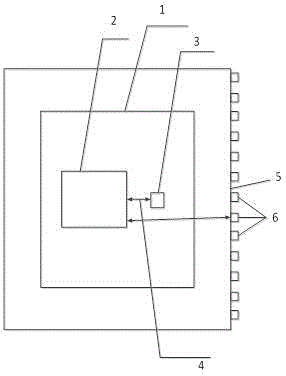

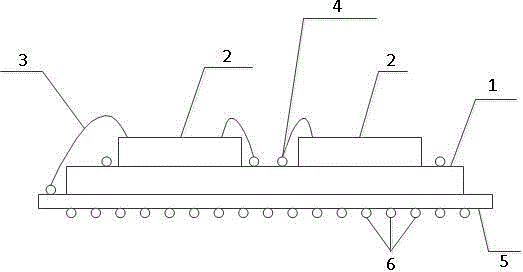

[0035] Such as figure 1 As shown, a common system-in-package chip in the prior art generally includes a first die 1, a second die 2, a bridge interface 3, a bridge circuit 4, a substrate 5 for placing the first die, and chip pins 6 . The second die 2 is located above the first die 1 , the substrate 5 is located below the first die 1 , and the chip pins 6 are led out from the first die 1 and / or the second die 2 and extend to the substrate 5 outside. The bridge interface 3 i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com