Buffer synchronization mechanism between double storage controllers

A dual-controller, synchronization mechanism technology used in memory addressing/allocation/relocation, input/output to record carrier, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

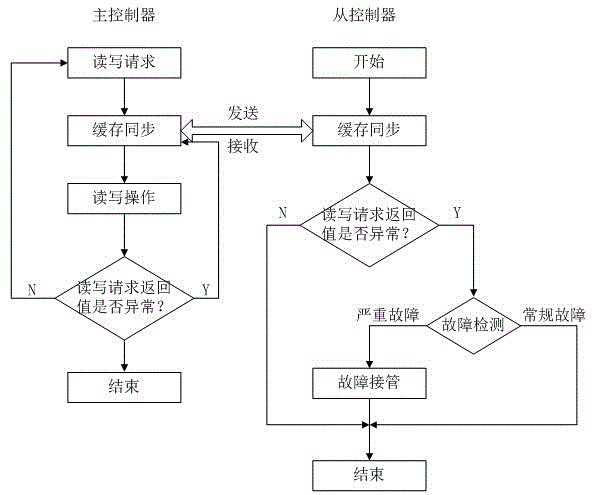

[0029] A cache synchronization mechanism between dual storage controllers of the present invention uses a 10G network connection between the dual storage controllers, and the mutual communication is completed by the heartbeat process and the cache synchronization process, specifically using the socket of the kernel layer;

[0030] The implementation of the cache synchronization function is divided into the implementation of the cache synchronization process and the heartbeat process; the cache synchronization process is divided into a master-slave work mode, and the initiation of the cache synchronization process is triggered by read and write requests and read and write exceptions in the master work mode. In the working mode, combined with the heartbeat process for fault detection and then transferred to the processing of the fault takeover thread; when the read and write returns to normal, it can respond to the client request without waiting for the completion of the cache fro...

Embodiment 2

[0035] A cache synchronization mechanism between dual storage controllers of the present invention uses a 10G network connection between the dual storage controllers, and the mutual communication is completed by the heartbeat process and the cache synchronization process, specifically using the socket of the kernel layer;

[0036] The implementation of the cache synchronization function is divided into the implementation of the cache synchronization process and the heartbeat process; the cache synchronization process is divided into a master-slave work mode, and the initiation of the cache synchronization process is triggered by read and write requests and read and write exceptions in the master work mode. In the working mode, combined with the heartbeat process for fault detection and then transferred to the processing of the fault takeover thread; when the read and write returns to normal, it can respond to the client request without waiting for the completion of the cache fro...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More