A System-on-Chip Bus with Non-isochronous Transfer Structure

A system-on-chip and bus technology, applied in the direction of instruments, electrical digital data processing, etc., can solve the problem of priority devices not getting the right to use the bus, and achieve the effect of reducing resource consumption, small hardware overhead, and ensuring real-time performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

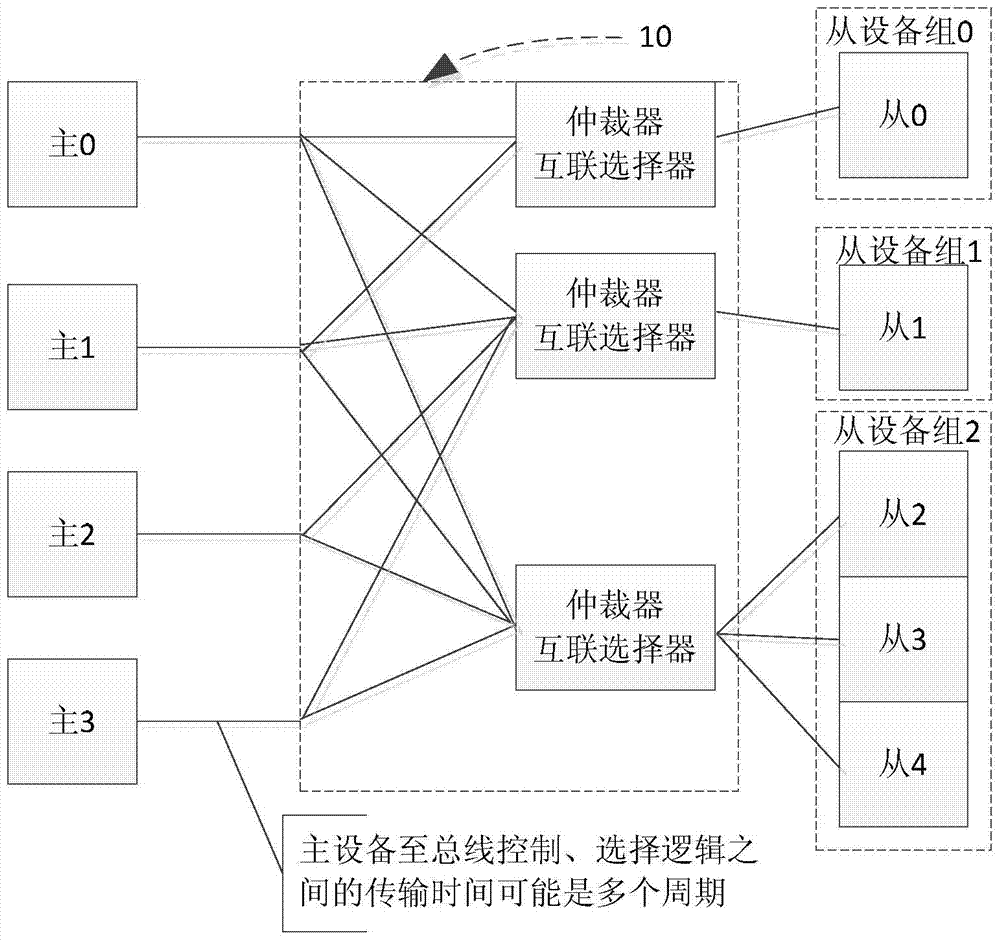

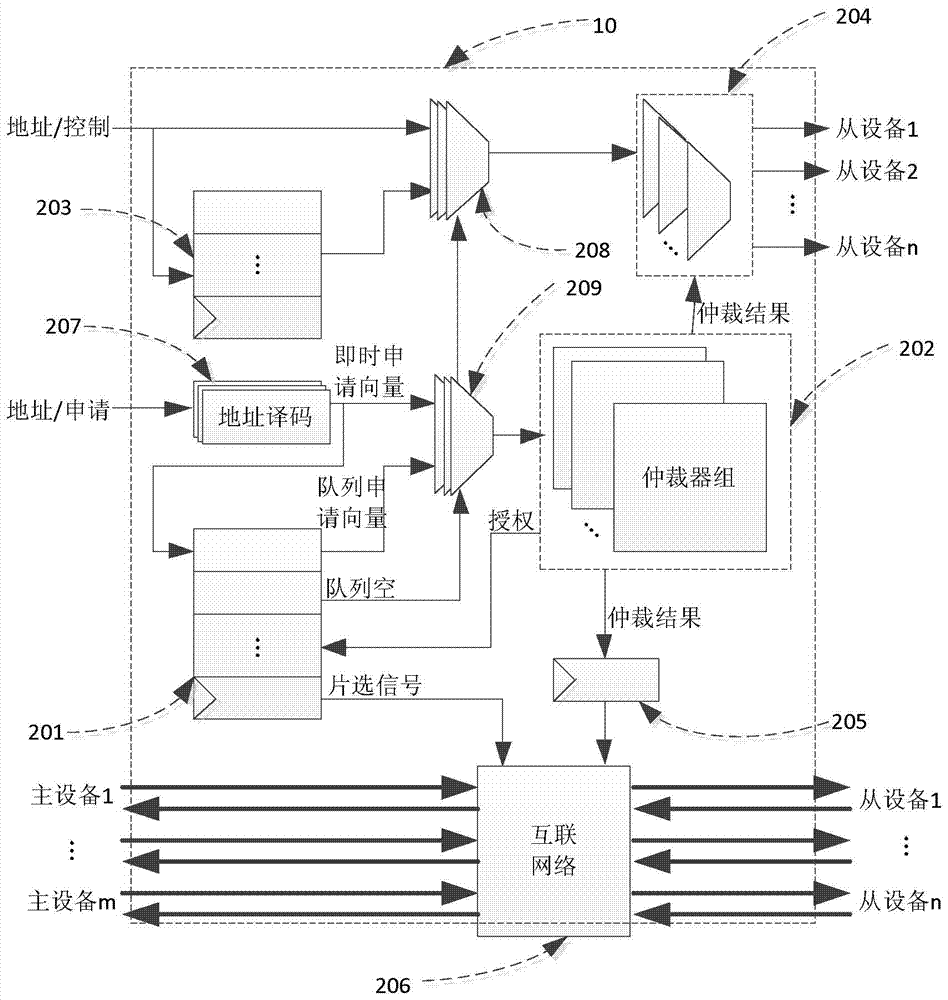

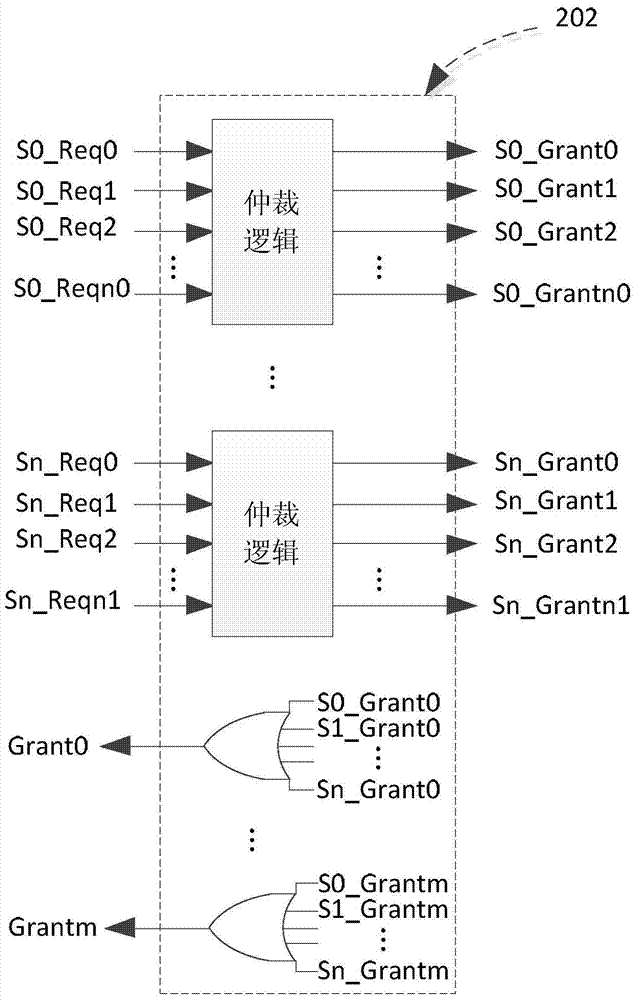

[0031] The invention provides a system-on-chip bus, which includes a request priority queue, an arbiter group, an address and control signal selector, an interconnection network, and an address decoder; a master device sends a bus request signal to the address decoder, and sends a corresponding The address signal and control signal are sent to the address and control signal selector; the address decoder sends an immediate application vector to the arbitrator group and the request priority queue according to the bus request signal; the request priority queue latches the application signal to generate a chip select signal , and send the chip select signal to the Internet, and at the same time, give the application vector of each slave device group according to the first-in-first-out principle, and the queue empty directly selects the result of the address decoder as the application signal of the current cycle and sends it to the arbitrator group ; The arbitrator group sends an ar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More