Preparation method of array substrate, array substrate, display panel and display device

A technology for array substrates and display panels, applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve the problems of complex process and high cost, achieve cost reduction, reduce requirements, control precision, and save patterning process Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

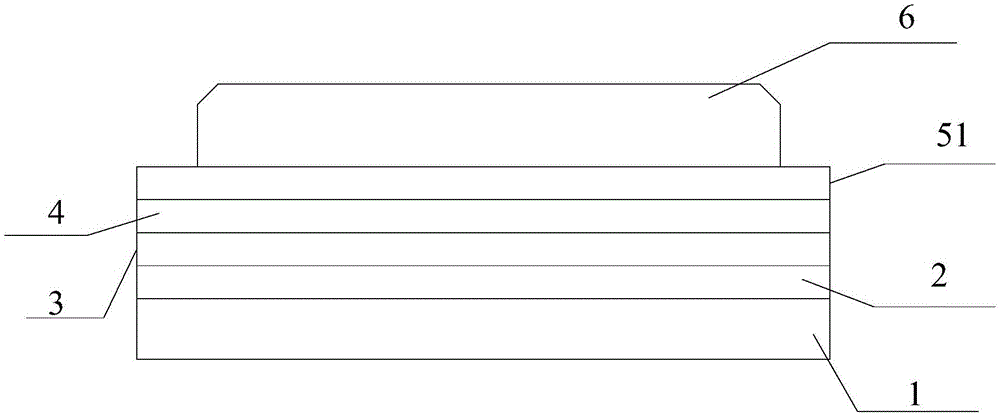

[0040] Such as figure 1 As shown, this embodiment provides a method for preparing an array substrate, including the following steps:

[0041] A step of forming patterns of an amorphous silicon layer and a polysilicon layer arranged at intervals by using the same mask plate.

[0042] In the preparation method of the array substrate in this embodiment, since the light-shielding layer and the active layer of the array substrate are patterned by using the same mask, the number of masks is saved, the one-step patterning process is saved, and the cost is reduced; At the same time, there is no need to consider the alignment problem in the patterning process, which reduces the requirements for equipment and control accuracy.

[0043] Specifically, the following steps can be used to prepare the array substrate:

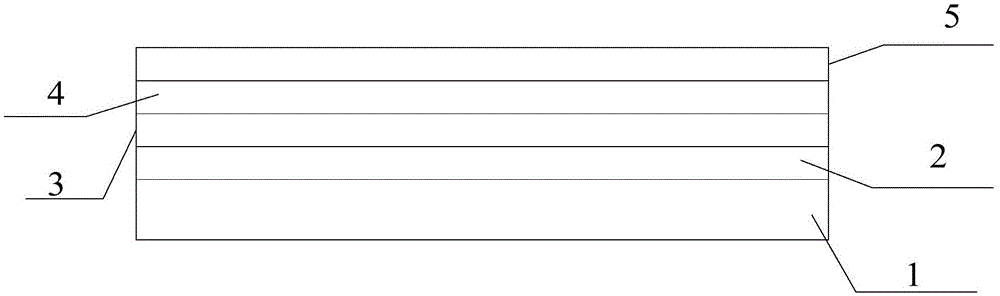

[0044] S1: a step of sequentially depositing a first buffer layer, a first amorphous silicon layer, a second buffer layer, and a second amorphous silicon layer on the substr...

Embodiment 2

[0059] This embodiment provides another method for preparing an array substrate. Specifically, the following steps can be used to prepare the array substrate:

[0060] S1: a step of sequentially depositing a first buffer layer, a first amorphous silicon layer, a second buffer layer, and a second amorphous silicon layer on the substrate;

[0061] Such as figure 1As shown, a first buffer layer 2, a first amorphous silicon layer 3, a second buffer layer 4, and a second amorphous silicon layer 5 are sequentially deposited on a substrate 1,

[0062] It should be understood that the above-mentioned functional layer can be prepared by plasma-enhanced chemical vapor deposition, and the specific deposition method is within the scope of the prior art, and will not be repeated here.

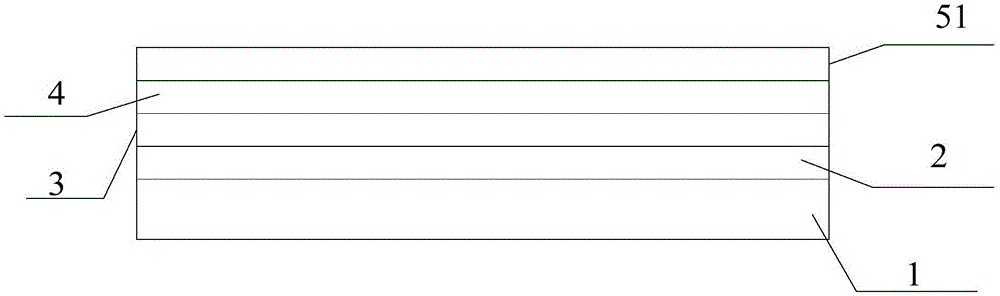

[0063] S2: a step of converting the second amorphous silicon layer into a polysilicon layer;

[0064] Such as figure 2 As shown, the second amorphous silicon layer 5 is subjected to dehydrogenation trea...

Embodiment 3

[0071] This embodiment provides an array substrate, which is prepared by using the above-mentioned method for preparing an array substrate.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More