Fixed-bit-width multiplier with high accuracy and low complexity properties

A low-complexity, fixed-bit technology, applied in instruments, electrical digital data processing, digital data processing components, etc., can solve the problems of high precision and complexity, large truncation errors, etc., and achieve the effect of high compensation accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

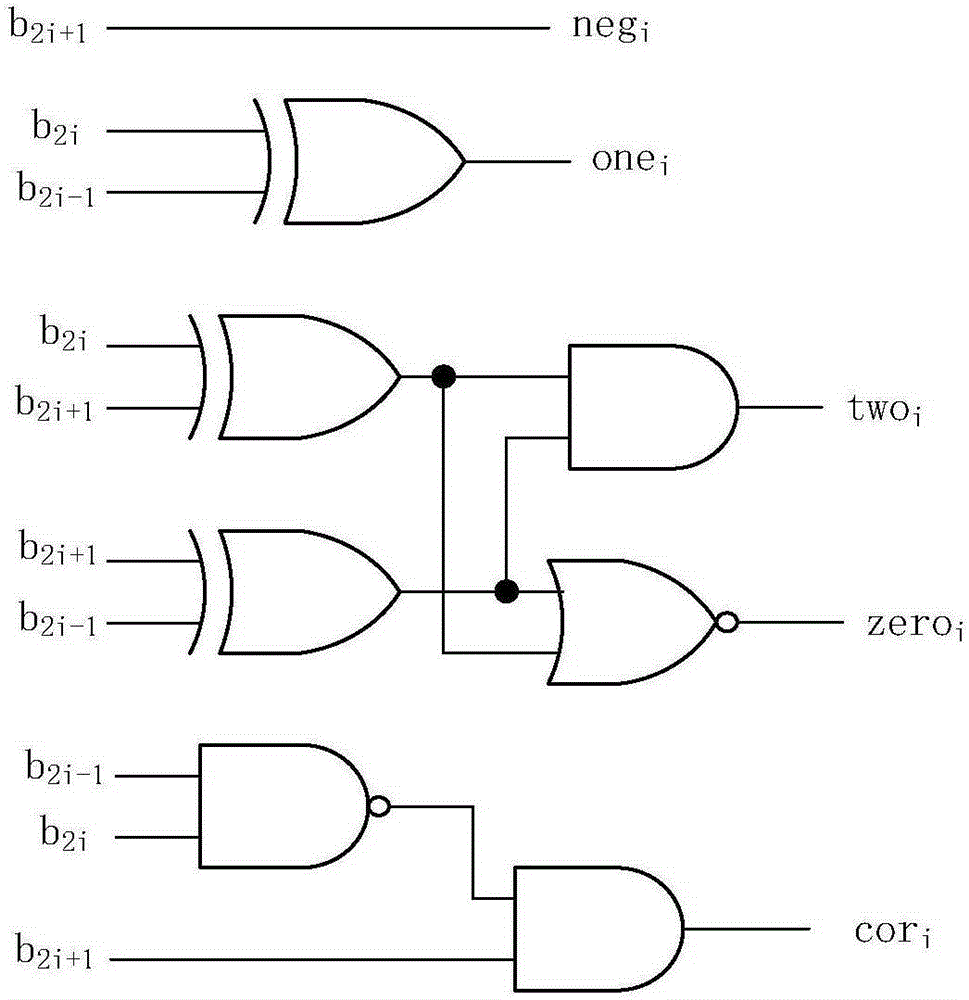

[0024] The present invention adjusts the probability mean value of the truncated partial product through the method of partial product array preprocessing, making it closer to the integer value, and at this time, using an integer to compensate the truncated partial product will have higher precision; Partial product, the compensation circuit is very simple, only need to consume few hardware resources.

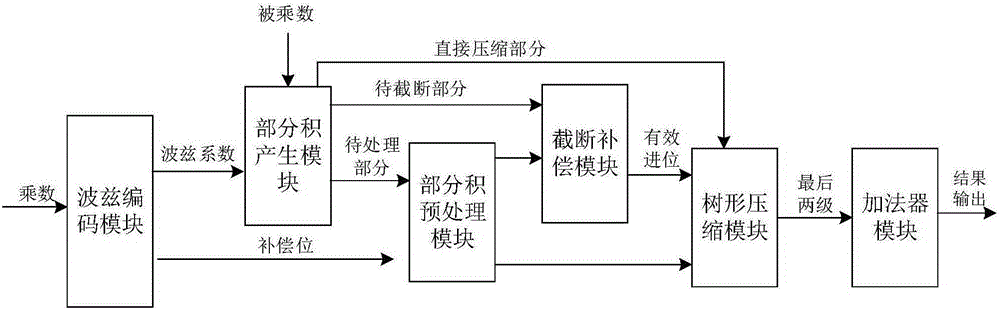

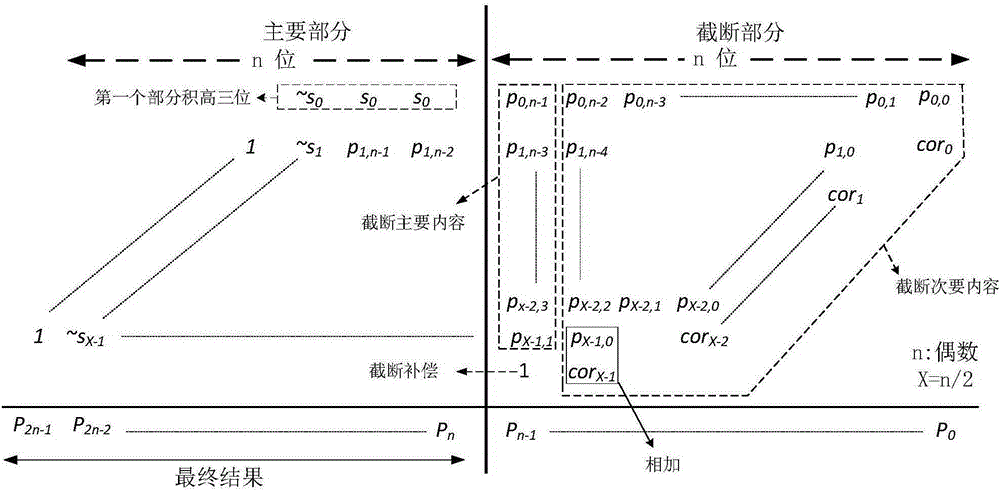

[0025] Such as figure 1 As shown, the fixed bit width multiplier includes: a Potz encoding module, a partial product generation module, a partial product preprocessing module, a truncation compensation module, a tree compression module, and an adder module. figure 2 It is a structural schematic diagram of the main part and the truncated part of the partial product array of the fixed bit width multiplier, wherein the main part is the reserved operation data, the truncated part is the data that needs to be truncated, and the truncated main content in the truncated part is also t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More